╬ĎϬÎ÷24HĐuÁ─ĽršŐ~Áź╬ĎĎ╗Í▒DEBUG~Ď╗Í▒Ë├▓╗│÷üÝ~

╬ĎXilinx ISE 8.2i▄Ťˇw~

ŇłĽ■Á─╚╦Ä═╬Ď┐┤Ď╗¤┬──│÷ňe┴╦~Íx

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity CLOCK_00_60 is

Port ( CLK : in STD_LOGIC;

RESET : in STD_LOGIC;

ENABLE : out STD_LOGIC_VECTOR (6 downto 0);

SEGMENT : out STD_LOGIC_VECTOR (6 downto 0));

end CLOCK_00_60;

architecture Behavioral of CLOCK_00_60 is

signal SCAN_CLK :STD_LOGIC;

signal COUNT_CLK :STD_LOGIC;

signal DECODE_BCD :STD_LOGIC_VECTOR (3 downto 0);

signal mineable :STD_LOGIC;

signal hreable :STD_LOGIC;

signal POSITION:STD_LOGIC_VECTOR (6 downto 0);

signal DIVIDER:STD_LOGIC_VECTOR (29 downto 1);

signal COUNT_BCD:STD_LOGIC_VECTOR (23 downto 0);

begin

-------------------------------------------------

process (CLK,RESET)

begin

if RESET = '0' then

DIVIDER <= ( others => '0');

elsif CLK' event and CLK = '1' then

DIVIDER <= DIVIDER + 1 ;

end if;

end process;

COUNT_CLK<=DIVIDER(24);

SCAN_CLK<=DIVIDER(15);

------------------------------------------------├Ű

process(RESET,SCAN_CLK)

begin

if RESET = '0' then

COUNT_BCD <= ( others => '0');

elsif SCAN_CLK' event and SCAN_CLK = '1' then

if COUNT_BCD(3 downto 0)= x"9" then

COUNT_BCD(3 downto 0)<= x"0";

COUNT_BCD(7 downto 4)<= COUNT_BCD(7 downto 4)+1;

else

COUNT_BCD(3 downto 0)<= COUNT_BCD(3 downto 0)+1;

end if;

end if;

end process;

mineable <= '1' when COUNT_BCD(7 downto 0) = x"59" else '0';

----------------------------------------------------------ĚÍ

process(RESET,SCAN_CLK)

begin

if RESET = '0' then

COUNT_BCD <= ( others => '0');

if mineable = '1' then

elsif SCAN_CLK' event and SCAN_CLK = '1' then

if COUNT_BCD(11 downto 8)= x"9" then

COUNT_BCD(11 downto 8)<= x"0";

COUNT_BCD(15 downto 12)<= COUNT_BCD(15 downto 12)+1;

else

COUNT_BCD(11 downto 8)<= COUNT_BCD(11 downto 8)+1;

end if;

end if;

end if;

end process;

hreable <= '1' when COUNT_BCD(15 downto 8) = x"59" else '0';

-------------------------------------------------------------Ľr

process(RESET,SCAN_CLK)

begin

if RESET = '0' then

COUNT_BCD <= ( others => '0');

if mineable = '1' and hreable = '1' then

elsif SCAN_CLK' event and SCAN_CLK = '1' then

if COUNT_BCD(19 downto 16)= x"9" then

COUNT_BCD(19 downto 16)<= x"0";

COUNT_BCD(23 downto 20)<= COUNT_BCD(23 downto 20)+1;

if COUNT_BCD(19 downto 16)= x"2" then

COUNT_BCD(23 downto 20)<= x"0";

else

COUNT_BCD(19 downto 16)<= COUNT_BCD(19 downto 16)+1;

end if;

end if;

end if;

end if;

end process;

process(RESET,SCAN_CLK)

begin

if RESET = '0' then

POSITION <= "1111110";

elsif SCAN_CLK' event and SCAN_CLK = '1' then

POSITION<="111111"&POSITION(0);

end if;

end process;

ENABLE<=POSITION;

-----------------------------------------------------------

process(POSITION,SCAN_CLK)

begin

case POSITION is

when "1111110" => DECODE_BCD <=COUNT_BCD(3 downto 0); --├Ű

when "1111101" => DECODE_BCD <=COUNT_BCD(7 downto 4); --├Ű

when "1111011" => DECODE_BCD <=COUNT_BCD(11 downto 8); --ĚÍ

when "1110111" => DECODE_BCD <=COUNT_BCD(15 downto 12); --ĚÍ

when "1101111" => DECODE_BCD <=COUNT_BCD(19 downto 16); --Ľr

when "1011111" => DECODE_BCD <=COUNT_BCD(23 downto 20); --Ľr

when others => null;

end case;

end process;

with DECODE_BCD Select

SEGMENT<= "1000000" when X"0",

"1111001" when X"1",

"0100100" when X"2",

"0110000" when X"3",

"0011001" when X"4",

"0010010" when X"5",

"0000010" when X"6",

"1111000" when X"7",

"0000000" when X"8",

"0010000" when X"9",

"1111111" when others;

end Behavioral;

]]>

sbit LED=P1^1;

void Init_Timer0(void)

{

TMOD = 0x01;

TH0=0x3C; /* Init value */

TL0=0xB0;

EA=1; /* interupt enable */

ET0=1; /* enable timer0 interrupt */

TR0=1; }

main()

{

tt=0;

Init_Timer0();

do{

TH0=0x3C; /* Init value */

TL0=0xB0;

LED=~LED;

tt++;

if(tt==2000)

{

LED=~LED;

tt=0;

}//ÍŞ╩żč˘Ě┤¤Ó*/

}

while(!TF0);

×Ú╩▓├┤č˘▓╗─▄ÚWáq─ěúČ╩ă│╠đ˛│÷ćľţ}┴╦├┤úČćľţ}ď┌╩▓├┤ÁěĚŻúČŇłŞ▀╚╦ÍŞŘcĎ╗¤┬úČ▄Ť╝■Ě┬ŇŠ┐╔Ďď═Ę▀^úČÁź╩ăÁŻîŹ˛×░ň╔¤ż═Ť]Ëđč˘ÚWáqúČ×Ú╩▓├┤─ě]]>

Ď╗.┤ˇ╝Ď▓╗Ϭ├Ą─┐Á─łˇIT┼ÓËľ░ÓúČϬ¤╚ŻY║¤Ď╗¤┬Îď╝║Á─┼d╚ĄŘcúČ┐┤┐┤Îď╝║ÁŻÁÎ╩ă¤Ű│╔×ÚĎ╗éÇ╩▓├┤śËÁ─╚╦úČ▓╗ϬňeŇ`Á─ŇJ×ÚÎď╝║╩ăËő╦ŃÖC¤ÁÁ─═ČîWúČ▒╗╚╦╝Ď║÷ËĂÄÎżńúČż═ËđĎ╗ĚNĎď║ˇ▓╗Î÷IT║├¤˝ż═┬˝Ť]┴╦Îď╝║Á─╠ý┘xÁ──ăĚNŞđËXíúϬăđËŤúČ┼cĂńĆ─╩┬Ď╗éÇÎď╝║ި▒ż▓╗Şđ┼d╚ĄÁ─đđśIúČ▓╗╚š╗ě╝Ď└¤└¤îŹîŹ┤˘Í°úȤۤŰÎď╝║ż┐ż╣¤Ű│╔×Ú╩▓├┤śËÁ─╚╦üÝÁ─îŹď┌íúíúíú

Â■.┤_ÂĘ┴╦ĚŻ¤˛úČŤQÂĘÎď╝║Ϭłˇ▀@éÇ┼ÓËľ░ÓÁ─Ľr║˛úČż═ϬÚ_╩╝▀xô˝┼ÓËľ░Ó┴╦íú▀x┼ÓËľ░Ó▀@éÇ╩┬ăÚúČĂńîŹćľţ}║▄ç└ÍěúČ╚š╣űňe▀x┴╦úČ║ˇ╣űĎ▓║▄ç└ÍěíúČFď┌╩└├Š╔¤Ëđ║▄ÂÓ┼ÓËľ░ÓúČÁŻÁÎłˇ──éÇ─ěú┐ϲ×Ú╬ĎÍ╗Î÷▀^â╔╝Ď┼ÓËľÖCśőúČĎ╗éÇ╩ă║ú═Č┐Ă╝╝úČ┴Ý═ÔĎ╗éÇż═╩ă▀_â╚┐Ă╝╝úČż═▀@â╔╝Ď┼ÓËľÖCśő╬Ď║ćć╬Á─ŇfĎ╗¤┬╬ĎÎď╝║Á─┐┤ĚĘ░╔úČâH╣ę═ČîWéâůó┐╝íú

╩Τ╚╬ĎŇf¤┬║ú═Č┐Ă╝╝úČ▀@╝Ď┼ÓËľÖCśőúČď§├┤Ňf─ěúČËŤÁ├«ö│§╬ĎîW┴ĽăÂ╚Ű╩ŻÁ─Ľr║˛úČĆ─51--avr--arm--fpga Ë├┴╦2─ŕúČîŹ┤˛îŹÁ─2─ŕúČŤ]╚ŇŤ]Ď╣Á─îW┴ĽúČ▓┼ËđŘc╩Ňź@íú╦¨Ďď╬Ď╩ă║▄ăň│■ăÂ╚Ű╩ŻîW┴ĽÁ─ĚÂç˙Í«ĆV┤ˇíúď┌▀@▀ů╬ĎĎ▓╔ţ┐╠Á─ˇwĽ■ÁŻ┴╦╩▓├┤ŻđÎ÷đž┬╩úČ┼eéÇ└řÎË ║ú═Č┼ÓËľbootloaderÍ╗Ëđ4╣ŁŇnúČ°ăĎÍ╗ÍvŻÔviviÁ─ćóäË┤˙┤aúČ°╬Ď«ö│§─ěúČbootloaderÍđvivi/redboot/uboot╗Ę┴╦3đăĂ┌Đđż┐ ▓╗╩ăŇf╬ĎËđÂÓ┼ú▓ŠúČ╬ĎĎÔ╦╝╩ă 4╣ŁŇn─▄îWÁŻ╩▓├┤úČθ×Ú└¤ÄčúČ╬ĎËđĽr║˛Â╝ËXÁ├Îď╝║║▄┼ú▓ŠúČ«öĽrÎď╝║Ń@Đđ┴╦▀@├┤ż├Á─ľ|╬¸úČ╚šŻ˝Ż╠ŻoîW╔˙żË╚╗┐╔Ďďď┌▀@├┤Â╠Á─ĽrÚgâ╚├ô«aúČ▓╗ͬÁ└╩ă╬ĎÁ─Ż╠îW╦«ĂŻŞ▀▀Ç╩ă═ČîWÁ─ŻË╩▄─▄┴Ž║├íúŇf¤┬Äč┘Y┴Ž┴┐░╔úČ╬Ď╩ăĎ╗«ůśIż═Í▒ŻË╚ą▄Ť╝■╣ź╦żÎ÷ITÚ_░lÁ─úČ▀@ĚŻ├ŠŻŤ˛×¤Ó«öěSŞ╗úČÎ÷┴╦Ëđ6éÇ─ŕţ^┴╦úČ╬Ďż═¤Ű┤˛╦ŃŞ─đđĆ─╩┬Ż╠Äč▀@éÇđđśIúČÎţŻK╩ă║ú═Č│╔ż═┴╦╬Ď▀@éÇ뢤ŰúČď┌┤╦╬ĎĎ▓Ěă│úŞđÍx║ú═Č┐Ă╝╝íúĂń╦űËđÄÎéÇ└¤Äč╬Ďż═▓╗ŞĎ╣žżS┴╦úČ╣ĄÎ¸1─ŕÁ─linux+armÁ─╣Ą│╠Äčż═▒╗╦űéâŇđ╩Ň▀^╚ąÎ÷ÍvÄčúČ╬ĎĎ▓ď°ŻŤÎ¸×Ú├Šďç╣┘├Šďç▀^úČŰm╚╗╦űéâĎ▓║▄â×đŃúČÁź╩㯍˛×Űy├ÔĽ■Ëđđę▓╗ÎŃíúď°ŻŤÁ─│đÍZ─ŕđŻ10╚fúČĎÍ╗˛╩ă░Řż═śIÁŻ├űáúČÂ╝âH╩ăđę│đÍZ┴T┴╦úČÄčŞÁţI▀MÚTúČđŮđđď┌éÇ╚╦úČ┤ˇ╝Ď▓╗Ϭ͸Ë^ŇJ×ÚÍ╗ϬüÝ┴╦ż═┐¤ÂĘŰx├űá▓╗▀h┴╦úČĂńîŹ▀@ĚNË^Řc╩ă═ŕ╚źňeŇ`Á─íú

ď┘Ňf¤┬▀_â╚┐Ă╝╝░╔úČ╬Ď╩ăËXÁ├▀@╝Ď╩ă║▄▓╗ňeÁ─úČ╬ĎŻ^]Ëđď┌▀@└´Î÷ĆVŞŠÁ─ĎÔ╦╝úČÍ╗╩ăĹ{┴╝đ─ď┌Ňfďĺíú╬Ďď┌▀@▀ůĎ▓┤ř┴╦┤ˇŞ┼┐ý2─ŕ┴╦úČ┐éÁ─üÝŇf╬Ď╩ă║▄ŁMĎÔÁ─úČď┌▀@└´ËđĎ╗╚║║▄â×đŃÁ─═Č╩┬úĘŻ^ĚăŇf║ú═Č▓╗â×đŃúęúČ30ÂÓéÇ═Č╩┬Â╝╩ăüÝÎď├└ç°íó╝Ë─├┤ˇÁ─║ú═Ô┴˘îW╚╦ćTúČÂ╝Í┴╔┘Ëđ5─ŕĎď╔¤Ć─śIŻŤ˛×║═ÝŚ─┐Ú_░lŻŤ˛×úČ┤ˇÄčŇf▓╗╔¤úČÁź╩ăîú╝Ď┐¤ÂĘ▓╗ÎŃ×Ú▀^íú°ăĎ▀@▀ůÁ─├┐Ď╗╬╗îWćTÁ─îW┴ĽŻŤÜvË╔Ď╗¤Á┴đîú╝ĎÍŞîžÁ─ú║5í¬8╝╝đgîú╝Ďô˙╚╬║╦đ─╩┌Ňn└¤Äčú╗1╬╗ÝŚ─┐ŻŤ└Ý╚ź│╠Ţoîžú╗1╬╗░Ó͸╚╬╚ź│╠╣▄└Ýú╗1╬╗┬ÜśI╦ě┘|┼ÓËľÄčÍŞîžú╗1╬╗┬ÜśI░lŇ╣ţÖćľÍŞîžíó═Ă╦]ż═śIú╗10ÂÓ╬╗├űáĎ╗żÇîú╝Ď├Š╩┌ÍŞŘc╝╝đg║═ăˇ┬Üíúíúíúíúď┌▀@▀ůż═╩ăËXÁ├ˇw¤Á╠ěäe║├úČ║▄▀z║Â║ˇ├ŠĎ˛×ÚäeÁ─ďşĎ˛╬ĎŤ]Ëđ└^└mď┌▀@▀ůÎ÷¤┬╚ąúČ╗ě¤ŰĎ╗¤┬ď┌▀_â╚Á──ăâ╔─ŕúČ║▄╩ăđ└╬┐íúíúíú╦¨Ďď╬ĎĎ▓╩ă║▄═Ă╦]╚ą▀_â╚Á─úČŰm╚╗═ČśËÂ╝╩ă│đÍZ▀M├űáúČÁź╩ăď┌▀@▀ůîW┴ĽÍ«║ˇúČ╚š╣ű─ŃŇŠÁ─║▄Ë├đ─úČ─ŃŇŠÁ─Űx├űáÍ╗ËđĎ╗▓ŻÍ«▀bíú

╚ř.ŇJŇŠîW┴Ľíú╝╚╚╗▀xô˝łˇ┴╦▀@éÇ┼ÓËľ░ÓúȤÓđ┼┤ˇ╝ĎÁ─│§ÍďÂ╝╩ă║▄║├Á─úČÂ╝╩ă¤ŰîWËđ╦¨Ë├úČîWËđ╦¨×Úíú╦¨ĎďŇJŇŠ╩ă▒ěÝÜÁ─úČϬËđłď│Í▓╗đŞÁ─ĎŃ┴ŽúČĎ╗ÂĘ▓╗─▄ŢpĐďĚ┼ŚëúČ╬ĎĎŐ▀^║▄ÂÓîWćTäéÚ_╩╝îWÁ─Ľr║˛Â╝╩ă▄P│¨ŁMÍżÁ─úČîW┴ĽŰy├Ô▒╚Ţ^┐Ţď´úČ║ˇ├Š┐╔─▄╩ăłď│Í▓╗¤┬üÝ┴╦░╔úČ╔¤▀^ÄÎéÇđăĂ┌Á─ŇnÍ«║ˇż═ď┘Ď▓Ť]ĎŐ▀^╦űÁ─╔ÝË░úČ│ř┴╦═´¤ž▀Ç╩ă═´¤žíúíúíú╝╚╚╗┤ˇ╝ĎÂ╝Ż╗┴╦ňXúČ×Ú┴╦▀@éÇňXúČ×Ú┴╦Ż╗ňXÁ─ŞŞ─ŞúȤú═ű┤ˇ╝ĎÂ╝─▄벳ď│ͤ┬üÝúČ▓╗ŻŤÜv´LËŕď§─▄ĎŐ▓╩║šúČ║╬Ťr┤ˇ╝Ď╩ăď┌Ď╗éÇ║▄║├Á─şhż│«öÍđúČ╬Ř╚íͬÎRíúíúíú¤ú═ű┤ˇ╝Ď─▄ë˛Ňń¤ž▀@śËĎ╗éÇÖCĽ■íú

Ďď╔¤ż═╩ă╬ĎÁ─Ď╗đęŻĘÎh║═¤ŰĚĘúČ┐╔─▄ËđđęÍ╗╩ă╬ĎÁ─Ď╗├ŠÍ«ď~úČÁź╩ă╬ĎÍ╗╩ăĎď╬Ďď°ŻŤ┐┤ÁŻÁ─ŻŤÜv▀^Á─╩┬îŹŇfďĺíú¤ú═ű¤Űłˇ┼ÓËľ░ÓÁ─═ČîWúČϬ▓┴┴┴Đ█żŽúČ▀xîŽ┼ÓËľÖCśőú╗ĎĐŻŤłˇ┴╦┼ÓËľ░ÓÁ─═ČîWúČÂ╝─▄ë˛┤˛Ă12ĚÍÁ─żź╔˝úČ║├║├îW┴ĽúČĎď║ˇ▀MĎ╗╝ĎÎď╝║đ─âxÁ─áśIúČ│╔×ÚáśIÍđÁ─Íđ┴¸ÝĂͨíú]]>

ĎÔ╬ÂÍ°─ŃDMÁ─bootloader│╠đ˛ĎĐŻŤ▒╗ĂĂë─╗˛Ň▀äh│řúí

╩Τ╚úČ─ŃϬ┼¬Â«╩▓├┤╩ăJTAG?

1ú║úáJTAG(Joint Test Action Group;┬ô║¤ťyďçđđäËđíŻM)╩ăĎ╗ĚNç°ŰHś╦ť╩ťyďçůfÎhúĘIEEE 1149.1╝Š╚ŢúęúČ͸ϬË├Ë┌đżĂČâ╚▓┐ťyďçíúČFď┌ÂÓöÁÁ─Ş▀╝ëø╝■Â╝Íž│ÍJTAGůfÎhúČ╚šDSPíóFPGAø╝■Á╚íúś╦ť╩Á─JTAGŻË┐┌╩ă4żÇú║TMSíóTCKíóTDIíóTDOúČĚÍäe×Ú─ú╩Ż▀xô˝íóĽršŐíóöÁô■Ţö╚Ű║═öÁô■Ţö│÷żÇíúđlĎĽ░lčř┬ô├╦Ňôë»$ g- `4 z; v- q `

TAGÎţ│§╩ăË├üÝîŽđżĂČ▀MđđťyďçÁ─úČJTAGÁ─╗¨▒żďş└Ý╩ăď┌ø╝■â╚▓┐ÂĘ┴xĎ╗éÇTAPúĘTest Access Port;ťyďçďLćľ┐┌úę═Ę▀^îúË├Á─JTAGťyďç╣Ąż▀îŽ▀Mđđâ╚▓┐╣ŁŘc▀MđđťyďçíúJTAGťyďçď╩ďSÂÓéÇø╝■═Ę▀^JTAGŻË┐┌┤«┬ôď┌Ď╗ĂúČđ╬│╔Ď╗éÇJTAGŠťúČ─▄îŹČF¸éÇø╝■ĚÍäeťyďçíúČFď┌úČJTAGŻË┐┌▀Ç│úË├Ë┌îŹČFISPúĘIn-System Programmable&#0;ď┌żÇżÄ│╠úęúČîŽFLASHÁ╚ø╝■▀MđđżÄ│╠íú

JTAGżÄ│╠ĚŻ╩Ż╩ăď┌żÇżÄ│╠úČ鸯y╔˙«a┴¸│╠Íđ¤╚îŽđżĂČ▀MđđţAżÄ│╠ČFď┘ĐbÁŻ░ň╔¤Ď˛┤╦°Ş─ÎâúČ║ć╗»Á─┴¸│╠×Ú¤╚╣╠ÂĘø╝■ÁŻŰŐ┬Ě░ň╔¤úČď┘Ë├JTAGżÄ│╠úČĆ─°┤ˇ┤ˇ╝Ë┐ý╣Ą│╠▀MÂ╚íúJTAGŻË┐┌┐╔îŽPSDđżĂČâ╚▓┐Á─╦¨Ëđ▓┐╝■▀MđđżÄ│╠8 Z: P6 `6 `- l- T, K" b8 t$ F

ż▀ËđJTAG┐┌Á─đżĂČÂ╝Ëđ╚š¤┬JTAGĎř─_ÂĘ┴xú║

TCKí¬í¬ťyďçĽršŐŢö╚Űú╗đlĎĽ░lčř┬ô├╦Ňôë»2 o# t3 z0 f$ I8 x% Z9 ^! ]; b

TDIí¬í¬ťyďçöÁô■Ţö╚ŰúČöÁô■═Ę▀^TDIŢö╚ŰJTAG┐┌ú╗đlĎĽ░lčř┬ô├╦Ňôë»' H; e4 R$ Y' B) w x( B3 W% C

TDOí¬í¬ťyďçöÁô■Ţö│÷úČöÁô■═Ę▀^TDOĆ─JTAG┐┌Ţö│÷ú╗

TMSí¬í¬ťyďç─ú╩Ż▀xô˝úČTMSË├üÝďOÍ├JTAG┐┌╠ÄË┌─│ĚN╠ěÂĘÁ─ťyďç─ú╩Żíú

┐╔▀xĎř─_TRSTí¬í¬ťyďçĆ═╬╗úČŢö╚ŰĎř─_úČÁ═ŰŐĂŻËđđžíú

║ČËđJTAG┐┌Á─đżĂČĚNţÉŢ^ÂÓúČ╚šCPUíóDSPíóCPLDÁ╚íúđlĎĽ░lčř┬ô├╦Ňôë») S$ l* H6 ~! ~+ W) r$ C; C

TAGâ╚▓┐ËđĎ╗éÇáţĹBÖCúČĚQ×ÚTAP┐ěÍĂøíúTAP┐ěÍĂøÁ─áţĹBÖC═Ę▀^TCK║═TMS▀MđđáţĹBÁ─Ş─ÎâúČîŹČFöÁô■║═ÍŞ┴ţÁ─Ţö╚ŰíúłD1×ÚTAP┐ěÍĂøÁ─áţĹBÖC┐˛łDíú; k$ {/ l) l& \' w9 w

2ú║ JTAGđżĂČÁ─▀ůŻšĺ▀├Ŕ╝─┤ŠĂ¸: Y8 `& e- p0 G* d7 m

TAGś╦ť╩ÂĘ┴x┴╦Ď╗éÇ┤«đđÁ─ĎĂ╬╗╝─┤ŠĂ¸íú╝─┤ŠĂ¸Á─├┐Ď╗éÇć╬ď¬ĚÍ┼ńŻoICđżĂČÁ─¤ÓŬĎř─_úČ├┐Ď╗éǬÜ┴óÁ─ć╬ď¬ĚQ×ÚBSCúĘBoundary-Scan Cellúę▀ůŻšĺ▀├Ŕć╬ď¬íú▀@éÇ┤«┬ôÁ─BSCď┌ICâ╚▓┐śő│╔JTAG╗ě┬ĚúČ╦¨ËđÁ─BSRúĘBoundary-Scan Registerúę▀ůŻšĺ▀├Ŕ╝─┤ŠĂ¸═Ę▀^JTAGťyďç╝Ą╗ţúČĂŻĽr▀@đęĎř─_▒ú│ÍŇř│úÁ─IC╣Ž─▄íúłD2×Úż▀ËđJTAG┐┌Á─ICâ╚▓┐BSRć╬ď¬┼cĎř─_Á─ŕP¤Áíú" Q/ f& }7 u; t

3 ú║ JTAGď┌żÇîĹFlashÁ─Ë▓╝■ŰŐ┬ĚďOËő║═┼cPCÁ─▀BŻËĚŻ╩Ż! E7 x5 d" c W6 }& O

Ďď║ČJTAGŻË┐┌Á─StrongARM SA1110×Ú└řúČFlash×ÚIntel 28F128J32 16MB╚Ţ┴┐íúSA1110Á─JTAGÁ─TCKíóTDIíóTMSíóTDOĚÍäeŻËPC▓ó┐┌Á─2íó3íó4íó11żÇ╔¤úČ═Ę▀^│╠đ˛îóîŽJTAG┐┌Á─┐ěÍĂÍŞ┴ţ║═─┐ś╦┤˙┤aĆ─PCÁ─▓ó┐┌îĹ╚ŰJTAGÁ─BSRÍđíúď┌ďOËőPCBĽrúČ▒ěÝÜîóSA1110Á─öÁô■żÇ║═ÁěÍĚżÇ╝░┐ěÍĂżÇ┼cFlashÁ─ÁěżÇżÇíóöÁô■żÇ║═┐ěÍÿǤÓ▀BíúϲSA1110Á─öÁô■żÇíóÁěÍĚżÇ╝░┐ěÍĂżÇÁ─Ďř─_╔¤Â╝ËđĂń¤ÓŬBSCúČÍ╗ϬË├JTAGÍŞ┴ţîóöÁô■íóÁěÍĚ╝░┐ěÍĂđ┼╠ľ╦═ÁŻĂńBSCÍđúČż═┐╔═Ę▀^BSCîŽĹ¬Á─Ďř─_îóđ┼╠ľ╦═ŻoFlashúČîŹČFîŽFlashÁ─▓┘θíúJTAGÁ─¤ÁŻy░ňďOËő║═▀BżÇŕP¤Á╚šłD3╦¨╩żíú2 B9 T" ~' @' v; m

4ú║ ═Ę▀^╩╣Ë├TAPáţĹBÖCÁ─ÍŞ┴ţîŹđđîŽFlashÁ─▓┘θ, k. D. j1 V! j

═Ę▀^TCKíóTMSÁ─ďOÍ├úČ┐╔îóJTAGďOÍ├×ÚŻË╩ŇÍŞ┴ţ╗˛öÁô■áţĹBíúJTAG│úË├ÍŞ┴ţ╚š¤┬ú║- z5 P; [$ \! _% j9 W

Ë├┤╦ÍŞ┴ţ▓╔śËBSCâ╚╚Ţ╗˛îóöÁô■îĹ╚ŰBSCć╬ď¬ú╗

EXTESTí¬í¬«öł╠đđ┤╦ÍŞ┴ţĽrúČBSCÁ─â╚╚Ţ═Ę▀^Ďř─_╦═ÁŻĂń▀BŻËÁ─¤ÓŬđżĂČÁ─Ďř─_úČ╬Ďéâż═╩ă═Ę▀^▀@ĚNÍŞ┴ţîŹČFď┌żÇîĹFlashÁ─ú╗

BYPASSí¬í¬┤╦ÍŞ┴ţîóĎ╗éÇĎ╗╬╗╝─┤ŠĂ¸▄ÄË┌BSCÁ─ĎĂ╬╗╗ě┬ĚÍđúČ╝┤âHËđĎ╗éÇĎ╗╬╗╝─┤ŠĂ¸╠ÄË┌TDI║═TDOÍ«Úgíú- y: \3 Y9 K; n8 K

ď┌PCBŰŐ┬ĚďOËő║├║ˇúČ╝┤┐╔Ë├│╠đ˛¤╚îóîŽJTAGÁ─┐ěÍĂÍŞ┴ţúČ═Ę▀^TDI╦═╚ŰJTAG┐ěÍĂøÁ─ÍŞ┴ţ╝─┤ŠĂ¸Íđíúď┘═Ę▀^TDIîóϬîĹFlashÁ─ÁěÍĚíóöÁô■╝░┐ěÍĂżÇđ┼╠ľ╚ŰBSRÍđúČ▓óîóöÁô■Ši┤ŠÁŻBSCÍđúČË├EXTESTÍŞ┴ţ═Ę▀^BSCîóîĹ╚ŰFlashíú-- DM500S,DM800HD,DM╣▓¤Ý,Íđđl,╦╣żS┐╦╠ýżÇ,│╔Â╝đlđăŰŐĎĽ░▓Đb,hibox,openbox,░┘▓ř525,░┘▓ř222,ak47,icool 2g,138,adbox,Íđż┼,öÁ┤aÁ═Â╦ÖC,╦ç╚A,╚A╚╦,░╦ăđĎ╗,╦─ăđĎ╗,╣ŽĚÍø -->! U7 c. t9 x- ?2 C! [6 T$ }

5ú║ ▄Ť╝■żÄ│╠

ď┌żÇîĹFlashÁ─│╠đ˛Ë├Turbo CżÄîĹíú│╠đ˛╩╣Ë├PCÁ─▓óđđ┐┌úČîó│╠đ˛═Ę▀^║ČËđJTAGÁ─đżĂČîĹ╚ŰFlashđżĂČíú│╠đ˛¤╚îŽPCÁ─▓ó┐┌│§╩╝╗»úČîŽJTAG┐┌Ć═╬╗║═ťyďçúČ▓óÎxFlashúČ┼đöÓ╩ăĚ˝╝ËŠiíú╚š╝ËŠiúČ▒ěÝܤ╚ŻÔŠiúČĚŻ┐╔▀Mđđ▓┘θíúîĹFlashÍ«ă░úČ▒ěÝÜîŽĂń¤╚▓┴│říúîóJTAGđżĂČďOÍ├ď┌EXTEST─ú╩ŻúČ═Ę▀^PCÁ─▓ó┐┌úČîó─┐ś╦╬─╝■═Ę▀^JTAGîĹ╚ŰFlashúČ▓óď┌čřîĹ═ŕ│╔║ˇ▀Mđđđú˛×íú│╠đ˛Í¸┴¸│╠╚šłD4╦¨╩żíú

═Ę▀^JTAGÁ─ÎxđżĂČIDÎË│╠đ˛╚š¤┬ú║-- DM500S,DM800HD,DM╣▓¤Ý,Íđđl,╦╣żS┐╦╠ýżÇ,│╔Â╝đlđăŰŐĎĽ░▓Đb,hibox,openbox,░┘▓ř525,░┘▓ř222,ak47,icool 2g,138,adbox,Íđż┼,öÁ┤aÁ═Â╦ÖC,╦ç╚A,╚A╚╦,░╦ăđĎ╗,╦─ăđĎ╗,╣ŽĚÍø -->+ ?6 y. Z; G. R$ \, U2 W4 R

void id_command(void)+ T& B7 P4 L3 R/ x/ h+ ^- O- Q2 }

putp(1,0,IP); //Run-Test/Idle;╩╣JTAGĆ═╬╗-- DM500S,DM800HD,DM╣▓¤Ý,Íđđl,╦╣żS┐╦╠ýżÇ,│╔Â╝đlđăŰŐĎĽ░▓Đb,hibox,openbox,░┘▓ř525,░┘▓ř222,ak47,icool 2g,138,adbox,Íđż┼,öÁ┤aÁ═Â╦ÖC,╦ç╚A,╚A╚╦,░╦ăđĎ╗,╦─ăđĎ╗,╣ŽĚÍø -->5 L' S: h- X' C7 J. l2 W

putp(1,0,IP); //Run-Test/Idle

putp(1,0,IP); //Run-Test/Idlewww.lztvro.com$ D% o/ z5 c, A% W; h. B0 u

putp(1,0,IP); //Run-Test/Idle

putp(1,1,IP);-- DM500S,DM800HD,DM╣▓¤Ý,Íđđl,╦╣żS┐╦╠ýżÇ,│╔Â╝đlđăŰŐĎĽ░▓Đb,hibox,openbox,░┘▓ř525,░┘▓ř222,ak47,icool 2g,138,adbox,Íđż┼,öÁ┤aÁ═Â╦ÖC,╦ç╚A,╚A╚╦,░╦ăđĎ╗,╦─ăđĎ╗,╣ŽĚÍø -->' a$ B# b: _- ?( j

putp(1,1,IP); //▀xô˝ÍŞ┴ţ╝─┤ŠĂ¸www.lztvro.com% \. l4 l$ r* r, ?# l5 D3 _! @

putp(1,0,IP); //▓Âź@ÍŞ┴ţ╝─┤ŠĂ¸-- DM500S,DM800HD,DM╣▓¤Ý,Íđđl,╦╣żS┐╦╠ýżÇ,│╔Â╝đlđăŰŐĎĽ░▓Đb,hibox,openbox,░┘▓ř525,░┘▓ř222,ak47,icool 2g,138,adbox,Íđż┼,öÁ┤aÁ═Â╦ÖC,╦ç╚A,╚A╚╦,░╦ăđĎ╗,╦─ăđĎ╗,╣ŽĚÍø -->6 n% q ?/ `$ d( h: i

putp(1,0,IP); /ĎĂ╬╗ÍŞ┴ţ╝─┤ŠĂ¸

putp(0,0,IP); //SA1110JTAG┐┌ÍŞ┴ţÚLÂ╚5╬╗úČIDCODE×Ú01100

putp(1,0,IP);

putp(1,0,IP);:-- DM500S,DM800HD,DM╣▓¤Ý,Íđđl,╦╣żS┐╦╠ýżÇ,│╔Â╝đlđăŰŐĎĽ░▓Đb,hibox,openbox,░┘▓ř525,░┘▓ř222,ak47,icool 2g,138,adbox,Íđż┼,öÁ┤aÁ═Â╦ÖC,╦ç╚A,╚A╚╦,░╦ăđĎ╗,╦─ăđĎ╗,╣ŽĚÍø -->; f5 b+ o i8 {

putp(0,0,IP);! J; y+ w' [8 F. a+ r( r( s$ I

putp(0,0,IP);% P; ]& |9 g8 j/ \

putp(0,1,IP); //═╦│÷ÍŞ┴ţ╝─┤ŠĂ¸* J) q$ [; B+ Q; J8 m* m

putp(1,1,IP); //ŞŘđ┬ÍŞ┴ţ╝─┤ŠĂ¸úČł╠đđÍŞ┴ţ╝─┤ŠĂ¸ÍđÁ─ÍŞ┴ţ

putp(1,0,IP)ú╗ //Run-Test/Idle-- DM500S,DM800HD,DM╣▓¤Ý,Íđđl,╦╣żS┐╦╠ýżÇ,│╔Â╝đlđăŰŐĎĽ░▓Đb,hibox,openbox,░┘▓ř525,░┘▓ř222,ak47,icool 2g,138,adbox,Íđż┼,öÁ┤aÁ═Â╦ÖC,╦ç╚A,╚A╚╦,░╦ăđĎ╗,╦─ăđĎ╗,╣ŽĚÍø -->, C# H* h8 V7 l( p- y. ?& M

putp(1,0,IP); //Run-Test/Idlewww.lztvro.com6 Y( O/ q! t5 ]( U

putp(1,0,IP); //Run-Test/Idle

putp(1,1,IP);www.lztvro.com' _3 F1 F4 E2 m' q

putp(1,0,IP);

if(check_id(SA1110ID))

error_out("failed to read device ID for the SA-1110");đlĎĽ░lčř┬ô├╦Ňôë», S; k& p$ N& o0 [$ D7 l* x- ^

putp(1,1,IP); //═╦│÷öÁô■╝─┤ŠĂ¸' h! c" B/ e. p& z

putp(1,1,IP); //ŞŘđ┬öÁô■╝─┤ŠĂ¸

putp(1,0,IP); //Run-Test/Idle,╩╣JTAGĆ═╬╗

putp(1,0,IP); //Run-Test/Idle

putp(1,0,IP); //Run-Test/IdleđlĎĽ░lčř┬ô├╦Ňôë»+ k- G% x, N; ?9 S0 b; j6 {! l9 j: |

6 ú║ ŰŐ┬ĚďOËő║═żÄ│╠ÍđÁ─ÎóĎÔ╩┬ÝŚ

ó┘FlashđżĂČÁ─WEíóCEíóOEÁ╚┐ěÍĂżÇ▒ěÝÜ┼cSA1110Á─BSR¤Ó▀BíúÍ╗Ëđ▀@śËúČ▓┼─▄═Ę▀^BSR┐ěÍĂFlashÁ─¤ÓŬĎř─_íú-- DM500S,DM800HD,DM╣▓¤Ý,Íđđl,╦╣żS┐╦╠ýżÇ,│╔Â╝đlđăŰŐĎĽ░▓Đb,hibox,openbox,░┘▓ř525,░┘▓ř222,ak47,icool 2g,138,adbox,Íđż┼,öÁ┤aÁ═Â╦ÖC,╦ç╚A,╚A╚╦,░╦ăđĎ╗,╦─ăđĎ╗,╣ŽĚÍø -->8 ]! m( \5 N, h- e [' ^

ó┌JTAG┐┌┼cPC▓ó┐┌Á─▀BŻËżÇϬ▒M┴┐Â╠úČďşät╔¤▓╗┤ˇË┌15cmíú

ó█Flashď┌▓┴îĹ║═żÄ│╠Ľr╦¨đŔÁ─╣ĄÎ¸ŰŐ┴¸Ţ^┤ˇúČď┌▀xË├¤ÁŻyÁ─╣ęŰŐđżĂČĽrúČ▒ěÝÜ╝ËĎď┐╝Ĺ]íúwww.lztvro.com# c4 v: S F* W' g6 v# `2 {1 W

ó▄×Ú╠ߪ▀îŽFlashÁ─żÄ│╠╦┘Â╚úČ▒M┴┐╩╣TCK▓╗Á═Ë┌6MHzúČ┐╔żÄîĹčřîĹFlash│╠đ˛ĽrîŹČFíú

6 l: r2 w1 J: ?

6 l: r2 w1 J: ?╩▓├┤╩ăBootLoaderúČ╦ŘÁ─θË├╩ă╩▓├┤ú┐) |' B# C7 F2 k6 [2 F' H

Bootloader╩ăď┌▓┘θ¤ÁŻy▀\đđÍ«ă░ł╠đđÁ─Ď╗Â╬đí│╠đ˛íú═Ę▀^▀@Â╬đí│╠đ˛úČ╬Ďéâ┐╔Ďď│§╩╝╗»Ë▓╝■ďOéńíóŻĘ┴óâ╚┤Š┐ŇÚgÁ─Ë│╔ń▒ÝúČĆ─°ŻĘ┴ó▀m«öÁ─¤ÁŻy▄ŤË▓╝■şhż│úČ×ÚÎţŻKŇ{Ë├▓┘θ¤ÁŻyâ╚║╦Î÷║├ť╩éńíú+ N" u# c) }9 Q( r/ U3 `

îŽË┌ăÂ╚Ű╩Ż¤ÁŻyúČBootloader╩ă╗¨Ë┌╠ěÂĘË▓╝■ĂŻ┼_üÝîŹČFÁ─íúϲ┤╦úČÄÎ║§▓╗┐╔─▄×Ú╦¨ËđÁ─ăÂ╚Ű╩Ż¤ÁŻyŻĘ┴óĎ╗éÇ═ĘË├Á─BootloaderúČ▓╗═ČÁ─╠Ä└Ýø╝▄śőÂ╝Ëđ▓╗═ČÁ─Bootloaderíú

Bootloader▓╗ÁźĎ└┘çË┌CPUÁ─ˇw¤ÁŻYśőúČ°ăĎĎ└┘çË┌ăÂ╚Ű╩Ż¤ÁŻy░ň╝ëďOéńÁ─┼ńÍ├íúîŽË┌2ëK▓╗═ČÁ─ăÂ╚Ű╩Ż░ň°ĐďúČ╝┤╩╣╦Řéâ╩╣Ë├═ČĎ╗ĚN╠Ä└ÝøúČϬ¤ŰÎî▀\đđď┌Ď╗ëK░ňÎË╔¤Á─Bootloader│╠đ˛Ď▓─▄▀\đđď┌┴ÝĎ╗ëK░ňÎË╔¤úČĎ╗░ŃĎ▓Â╝đŔϬđŮŞ─BootloaderÁ─ď┤│╠đ˛íú

┐ý┐ý╚ąçLďçđŮĆ═─ŃDMÁ─Bootloader│╠đ˛úČüÝŇŘż╚─ŃÁ─DM500úí

-- DM500S,DM800HD,DM╣▓¤Ý,Íđđl,╦╣żS┐╦╠ýżÇ,│╔Â╝đlđăŰŐĎĽ░▓Đb,hibox,openbox,░┘▓ř525,░┘▓ř222,ak47,icool 2g,138,adbox,Íđż┼,öÁ┤aÁ═Â╦ÖC,╦ç╚A,╚A╚╦,░╦ăđĎ╗,╦─ăđĎ╗,╣ŽĚÍø --> {. m% \; W+ E$ |

-- DM500S,DM800HD,DM╣▓¤Ý,Íđđl,╦╣żS┐╦╠ýżÇ,│╔Â╝đlđăŰŐĎĽ░▓Đb,hibox,openbox,░┘▓ř525,░┘▓ř222,ak47,icool 2g,138,adbox,Íđż┼,öÁ┤aÁ═Â╦ÖC,╦ç╚A,╚A╚╦,░╦ăđĎ╗,╦─ăđĎ╗,╣ŽĚÍø --> {. m% \; W+ E$ |]]>

╩Τ╚úČîŽË┌RS232═ĘˏϬ┴╦ŻÔúČ╝┤ď┌232═ĘËŹ«öÍđúČí░-3V~-15Ví▒▒Ý╩ż▀ëŢő1úČí░+3V~+15Ví▒▒Ý╩ż▀ëŢő0íúČFď┌╬ĎéâüÝîŽŰŐ┬Ě▀MđđĚÍ╬÷Ď╗¤┬íú

¤┬├Š¤╚┐┤ć╬ĂČÖC▀@▀ůú║«öć╬ĂČÖCTXD2Â╦┐┌Ě┼╦═öÁô■ĽrúČ«ö×ÚÁ═ŰŐĂŻí░0í▒ĽrúČ╣Ô˝ţîž═ĘúČ+6VŻŤ▀^RXíóR52íóD13íóR51íó╣Ô˝ţ1úČ2─_ÁŻÁěđ╬│╔╗ě┬Ěíú┤╦╗ě┬ĚÎŔÍÁ┤ˇÍ┬×Ú2.2K+2.2K+1.6K=6KúČI=6/6K=1mAíúď┌▀@ĚNăÚŤr¤┬úČRX┤ˇŞ┼ď┌5.ÄÎVúČ╣╩PCÖCŻË╩Ň×Ú▀ëŢőí░0í▒íú┼cć╬ĂČÖC▀@▀ů░l╦═¤ÓĎ╗Í┬íúË╔Ë┌┤╦Ľr1mA×ÚŻěÍ╣úȲîäË▓╗┴╦░l╣ÔÂ■śO╣▄úČÁź─▄îž═Ęíú╣╩îŽTXŤ]ËđË░ÝĹíú

═Č└Ý«öTXD2×ÚŞ▀ŰŐĂŻí░1í▒ĽrúČIC14ŻěÍ╣úČRX×ÚÁ═ŰŐĂŻúČ+6ŻŤ▀^C21íóC20íóR52╗ěÁŻRXúČÎóĎÔG3Á─╬╗Í├úČ┤╦ĽrRXË╔Ë┌Ě┼ŰŐ╠ÄË┌ěôë║áţĹBúČ╣╩×Ú▀ëŢőí░1í▒úČ┼c░l╦═áţĹB¤ÓĎ╗Í┬íú

ŻË¤┬éz┐┤┐┤PCÖC▀@▀ůíú«öTX░l╦═í░0í▒úČśO×ÚŞ▀ŰŐĂŻĽrúČIC13îž═ĘúČRXD2×ÚÁ═ŰŐĂŻúČ╣╩×Úí░0í▒íú«öTX×Úí░1í▒úČ╝┤×Úí░-3~-15Ví▒ĽrúČ├¸´@IC13ŻěÍ╣°RXD2×ÚŞ▀ŰŐĂŻíú

┐éˇw╔¤ŇfúČRS232ż═╩ăĎ╗éÇŰŐĂŻŮDôQÁ─▀^│╠úČ▓╗╣▄╩ă╔¤├Š╦¨┤ţÁ─ŰŐ┬Ě▀Ç╩ăMAX232Â╝╩ăŰŐĂŻŮDôQíúÁźď┌Ň{ďçÁ─▀^│╠«öÍđúČ░lČFPCÖC░l╦═öÁô■ĽrúČć╬ĂČÖCŻË╩▄Á─╩ă░l╦═öÁô■Á─2▒ÂíúÍ╗ËđÍvŻË╩ŇÁŻÁ─öÁ│řĎď2▓┼─▄Á├ÁŻîŹŰH░l╦═Á─öÁô■íú

▀@Ď╗ćľţ}Ëđ┤řŻÔŤQíú]]>

tory burch shoes Quasi-dynamic high-fidelity real-time image capture and compres

MAC Cosmetics Cheap PE3293 high-performance PLL and its application _ of Chemist

p90x discount Heat Energy Meter Based on PIC Microcontroller Development of Chem]]>

<P>1íóËđĎ╗ÂĘÁ─╔¤żWĽrÚgúČ▓óăĎËđ¤▓Ügď┌żW╔¤▒ÝČFíú<br>2íó├┐éÇ╚╦Â╝┐╔Ďď╔ŕŇł│╔×Ú│╔×ÚČFËđ░ŠëKÁ─░ŠÍ¸úČ╝░ިô■ÎďĎĐÁ─¤▓║├╔ŕŇłđ┬Ú_░ŠëK│╔×Ú░ŠÍ¸íú<br>3íó▓╗Á├╔ŕŇł┼cÍđ╚A╚╦├˝╣▓║═ç°ĚĘ┬╔¤ÓÁÍË|Á─â╚╚Ţ░ŠëKú«<br>4íó╦¨ËđÁ─¤ŰÎ÷░ŠÍ¸Á─Â╝ď┌▀@└´Ş˙┘NŇf├¸íú<br>5íó╦¨Ëđ╔ŕŇł░ŠÍ¸Á─╚╦Ňł¤╚ď┌Îď╝║¤ŰÎ÷░ŠÍ¸Á─Ö┌─┐ÂÓ░lĎ╗đęËđârÍÁÁ─┘NúČď┘╔ŕŇłĽ■║├đęíúúĘ╚š╣űČFËđÖ┌─┐Ť]Ëđ▀m║¤─ŃÁ─úČ°ăĎĎ▓╩ăŰŐÎË╝░ŰŐ─XđđśIÁ─úČ┐╔Ďď¤╚╔ŕŇł░ŠÍ¸íúúę<br>6íóĚă│úÜgËşËđÎď╝║Á─«aĂĚÁ─╝░─▄¤ÁŻyŻÚŻBÎď╝║╦¨¤▓ÜgđđśIͬÎRÁ─╚╦ćT╝Ë╚Űíú<br>7íó░ŠÍ¸┐╔Ďďď┌Îď╝║╦¨╣▄Ö┌─┐░l▒ÝÎď╝║«aĂĚúĘ▒ěđŔ┼cÖ┌─┐¤ÓŕPúę<br>8íó▒ěÝÜ╩ý¤ĄżWŇżŻĘďO║═Îď╝║░Š├ŠÁ─â╚╚Ţíú<br>9íó▒ěÝÜ├┐╠ýŞŘđ┬╦¨ěôěč░Š├ŠÁ─â╚╚ŢúĘÎţ╔┘Ď╗ì╬─Ň┬╗˛▄Ť╝■úę║═ŻÔ┤╦ű╚╦╠ß│÷Á─ćľţ}íú<br>10íóÁăËŤŇŠîŹđŇ├űíóÁěÍĚíó▒żŇôë»idÁ╚</P>

<P><br>░ŠÍ¸ÖÓ¤Ů║═└űĎŠĚͤÝú║<br>1íó┐╔ôÝËđ▒żŇôë»Á─╚ź▓┐ÖÓ¤Ůú╗<br>2íó┐╔¤Ý╩▄▒żŇż«aĂĚÁ─│╔▒żâr╗˛┤˙└ÝârŞ˝úĘ│╔×Ú░ŠÍ¸2éÇď┬║ˇú╗<br>3íó¤Ý╩▄ÝŚ─┐║¤Î¸ÖCĽ■ú╗<br>4íóâפ╚═Ă╦]Ş▀đŻ╣ĄÎ¸ÖCĽ■ú╗<br>ËđĎÔŇ▀Ňł┼cŇżÚL┬ô¤Áú║emailú║<a target="_blank" >21control@21cn.com</A></P>

<P><br>ŇłîŽ┤╦╠ßÎhËđđ┼đ─║═┼d╚ĄÁ─┼ˇËĐŞ˙┘Níú<br></P><br><br><br><br>

<P>ŞŻ░ŠÍ¸╔ŕŇł▒ÝŞ˝ú║</P>

<P><br>==================================================================<br>─˙ď┌▒żŇôë»IDú║ <br>đďííííííííäeú║<br>Ϭ╔ŕŇłÁ─░Š├Šú║ <br>─┐ă░żËÎí│ă╩đú║<br>┬ÜśIĎď╝░╠ěÚLú║ <br>─˙Á─┬ô¤ÁĚŻ╩Żú║úĘQQ/ICQ/MSNÁ╚úę<br>╚Ňż¨╔¤żWĽrÚgú║<br>╩ăĚ˝Î÷▀^░ŠÍ¸ú║úĘ͸ϬͪĂń╦űÁ─Ňôë»úę<br>╩ýÎRÁ─░Š├Šú║úĘ▒żŇôë»╔¤Á─úę<br>==================================================================<br>─˙ŇJ×Ú░ŠÍ¸Á─┬Üěč╩ă╩▓├┤ú┐</P>

<P>==================================================================<br>─˙╔ŕŇłďô░Š░ŠÍ¸Á─ďö╝Ü└ÝË╔╩ă╩▓├┤ú┐<br>úĘ͸ϬŕU├¸─˙×Ú╩▓├┤ϬÎ÷ďô░Š░ŠÍ¸úČĎď╝░Îî╬Ďéâ¤Óđ┼úČ─˙Ëđ╣▄║├ďô░ŠÁ──▄┴Žúę</P>

<P>==================================================================<br>îŽ─˙╦¨╔ŕŇłÁ─░Š├ŠúČ─˙ŇJ×ÚŬďô╚š║╬░lŇ╣ú┐</P>

]]>

LED ˛îäËđżĂČÁ─äËĹBÝĹŬ╠ěđ﯍│ú▒╗║÷┬ďúČÁźůs╩ă¤Ó«öÍěϬÁ─Ď╗éÇ╠ěđďíúäËĹBÝĹŬË░ÝĹLED´@╩żĂ┴Á─Ë░¤˝┘|┴┐úČ╚š╗ĎŰAíóżÇđďÂ╚íóEMIíóđ┼┘çđďíúŰm╚╗▀@đę╠ěđď▒╦┤╦ÚgËđ╚í╔ßŕP¤Áú«Áź╩ă║├Á─˛îäËđżĂČŬďô─▄ë˛ď┌▀@đę╠ěđďÍđ╚íÁ├Ţ^╝ĐÁ─ĂŻ║Ôíú▒ż╬─îó╠ŻËĹäËĹBÝĹŬÁ─ÍěϬđď╝░LED˛îäËđżĂČ┼cŰŐ┬Ě░ňďOËő╝╝đgúČĎďůfÍ˙╣Ą│╠ÄčďOËő│÷Ë░¤˝┘|┴┐┴╝║├Á─´@╩żĂ┴íúś╦ ║× ˛îäËø Ż╗┴¸ÝĹŬú║═╗ĂĂ driver AC respanse overshoot

AC responses of LED drivers are critical but usually ignored in LED display applicationsú«AC responses affect the major performance of LED display panelsúČsuch as grayscalesúČ linearityúČ EMIúČ and reliabilityú« Although there is trade-off w ithin these requirementsúČ LED drivers can provide balanceú«This article will further explain the importance of the AC responses of LED drivers and PCB design techniques to help engineers to design LED panels with good grayscale images]]>

íííí

ííííđíă╔┴ßşçÁ─řłđżIIŞúşç├ď─ŃŰŐ─XúČ°▀@┼_ŰŐ─XŁMěôŢd╣Ž┬╩Ď▓▓╗│Č▀^20W

íííí

íííířłđżIIŞúşç├ď─ŃŰŐ─Xă░đ▒ĎĽłDíúˇwĚe┤ˇŞ┼║═Ď╗éÇ═ÔÍ├Ë▓▒P║đ▓ţ▓╗ÂÓíú

íííí

íííířłđżIIŞúşç├ď─ŃŰŐ─X║ˇđ▒ĎĽłDíú

íííí

ííííă░├Š░ň╔¤Ě┼Í├┴╦4éÇUSB2.0íóűť┐╦´LíóÂ˙ÖCíóżÇđďŢö│÷▓ň┐┌ú╗╝t═ÔIO┤░┐┌úČĎď╝░Ď╗ŻMÍŞ╩żč˘║═Ć═╬╗íóŰŐď┤Ú_ŕPíú

íííí

íííí║ˇ├Š░ň╔¤Ě┼Í├┴╦ŠI╩ˇ╣▓Ë├Á─PS2┐┌íóżW┐ĘRJ45íó´@╩żĂ¸─úöMŢö│÷íóĎĽţlSÂ╦íó┤«┐┌▓ňΨĎď╝░Í▒┴¸12VŰŐď┤▓ňΨ

íííí

íííířłđżIIŞúşç├ď─ŃŰŐ─XÁÎ├Š

íííí

ííííÁÎ├ŠÁ─ŃĹ┼ĂúČ╬Ďéâ─├ÁŻÁ─▀@┼_śËĂĚ┼ńÍ├▓ó▓╗Ş▀íú256Mâ╚┤Š/40GË▓▒P/666MHzÁ─řłđż2E╠Ä└Ýø

íííí

íííí▓│ř═ÔÜĄ║ˇÁ─ă░đ▒ĎĽłD

íííí

íííí▓│ř═ÔÜĄ║ˇÁ─ÁÎă░đ▒ĎĽłD

íííí

íííí

ííííNECÁ─USB2.0┐ěÍĂđżĂČ

íííí

ííííATI Radeon 7000M´@╩żđżĂČúČ┼ď▀ůÁ─đíĚŻëK╩ă16M DDR´@╩żâ╚┤ŠđżĂČíú

íííí

íííířłđż2E╠Ä└ÝøúČĎÔĚĘ░Űw┤˙╝Ë╣Ąíú▓╔Ë├90nm╣Ą╦çíú ▀@┐ţ╠Ä└Ýø╩«ĚÍ╣Ł─▄úČĚňÍÁ╣Ž┬╩âHËđ4WúČ▀@éÇâ×äŢÎîřłđż2EđżĂČ┐╔Ë├ţI˲┤ˇĚ¨═ěŇ╣íú řłđż2E╔¤ĚŻÁ─đżĂČ×ÚAltera Cyclone II FPGAúČ▀@╩ăĎ╗ţwČFł÷┐╔żÄ│╠ÚTŕç┴đđżĂČúČ ═Ę▀^żÄ│╠┐ěÍĂúČ▀@ţwđżĂČĂÁŻ┴╦Ď╗éÇ║ćć╬Á─▒▒ś˛đżĂČÁ─θË├íú

íííí]]>

Atom E600C¤Á┴đĐđ░l┤˙╠ľ×ÚStellartonúČŻ˝─ŕ9ď┬ĚŢÁ─IDF┤ˇĽ■╔¤╩Î┤╬╣źÚ_úČŻ˝╠ýätŇř╩Ż░l▓╝íúďô¤Á┴đîŹŰH╔¤ż═╩ăîóĎ╗ţw┤˙╠ľTunnel CreekÁ─Atom E600ăÂ╚Ű╩Ż╠Ä└Ýø║╦đ─┼cAltera FPGAĚÔĐbď┌Ď╗ţwđżĂČ╔¤íú╗¨Ë┌FPGAÁ─┐╔żÄ│╠╠ěđďúČ┐═ŢĆS╔╠┐╔îŽ▀@ţwÂ■║¤Ď╗╠Ä└Ýø▀Mđđ▓╗═ČÁ─┼ńÍ├úČĎďŁMÎŃ▓╗═ČŬË├Á─đŔϬíú

îŽË┌¤┬Ë╬ĆS╔╠üÝŇfúČ╩╣Ë├▀@ţwÂ■║¤Ď╗╠Ä└Ýø┐╔Ďď║ć▒ŃÁ─Ú_░l│÷ßśîŽ▓╗═Č╩đł÷đŔăˇÁ─ŬË├╠Ä└Ýø«aĂĚúČ▒╚╚š╣Ą┐ěÖCíó▒Ńöy╩Żßt»čďOéńíó═ĘËŹďOéńíóĎĽËX¤ÁŻyíóVOIPďOéńíóŞ▀đď─▄┐╔żÄ│╠▀ëŢő┐ěÍĂøíóăÂ╚Ű╩ŻËő╦ŃÖCÁ╚íú═ČĽrúČË╔Ë┌╩í╚ą┴╦×ÚĂń┤ţ┼ńFPGAÁ╚đżĂČÁ─▓ŻˇEúČ┐╔Ďď╣Ł╝sŰŐ┬Ě░ň┐ŇÚgúČ┐ěÍĂÄý┤Š║═│╔▒żúČ║ć╗»ÍĂďý▀^│╠úČ▓óăĎÍ╗đŔϬĎ└┘çĎ╗╝ĎĆS╔╠╠ß╣ęĚ■äŇíú

║╦đ─╝▄śő

Intel×Ú├Š¤˛ăÂ╚Ű╩Ż«aĂĚ╠ß╣ę7─ŕ╔˙├ŘÍ▄Ă┌Á─ÍĂďýÍž│ÍúČAtom E600C¤Á┴đČFËđ6┐ţđ═╠ľúČE665CTíóE645CTíóE665C║═E645Cîóď┌60╠ýâ╚╔¤╩đúČE625CT║═E625CätĽ■ď┌├¸─ŕĎ╗╝żÂ╚│÷ěŤíú╚ź¤Á┴đ«aĂĚÁ─ăžţwć╬ârď┌61ÁŻ106├└ď¬Í«Úgíú─┐ă░úČăÂ╚Ű╩Ż¤ÁŻyÚ_░l╔╠KontronĎĐŻŤ┐╔Ďď╠ß╣ę╗¨Ë┌Atom E600CÁ─╣Ą│╠śË░ňúČ├¸─ŕÂ■╝żÂ╚Ú_╩╝┴┐«aíú

đ═╠ľ┴đ▒Ý

Ú_░lĂŻ┼_

íííí đ┬Ď╗┤˙ FPGAÁ─╦┘Â╚ÎâÁ├ďŻüÝďŻ┐ý,├▄Â╚ÎâÁ├ďŻüÝﯪ▀,▀ëŢő┘Yď┤Ď▓ďŻüÝďŻÂÓíú─ă├┤╚š║╬▓┼─▄┤_▒ú╣Ž║─▓╗ŰS▀@đęĎ╗Ăď÷╝Ë─ěú┐║▄ÂÓďOËőż˝ô˝┐╔ĎďË░ÝŤÁŻyÁ─╣Ž║─,▀@đęż˝ô˝░Ř└ĘĆ─´@ĎŐÁ─ø╝■▀xô˝ÁŻ╝ÜđíÁ─╗¨Ë┌╩╣Ë├ţl┬╩Á─áţĹBÖCÍÁÁ─▀xô˝Á╚íú

íííí ×Ú┴╦ŞŘ║├Áě└ÝŻÔ▒ż╬─îóϬËĹŇôÁ─ďOËő╝╝ă╔×Ú╩▓├┤─▄ë˛╣Ł╩í╣Ž║─,╬Ďéâ¤╚îŽ╣Ž║─Î÷Ď╗éÇ║ćć╬ŻÚŻBíú

íííí ╣Ž║─░Ř║Čâ╔éÇϲ╦ěú║äËĹB╣Ž║─║═ýoĹB╣Ž║─íúäËĹB╣Ž║─╩ăÍŞîŽĂ¸╝■â╚Á─╚ŢđďěôŢd│ńĚ┼ŰŐ╦¨đŔÁ─╣Ž║─íú╦Ř║▄┤ˇ│╠Â╚╔¤╚íŤQË┌ţl┬╩íóŰŐë║║═ěôŢdíú▀@╚řéÇÎâ┴┐ÍđÁ─├┐éÇÎâ┴┐ż¨ď┌─˙Á──│ĚN┐ěÍĂÍ«¤┬íú

íííí äËĹB╣Ž║─ = ŰŐ╚Ţí┴ŰŐë║2í┴ţl┬╩

íííí ýoĹB╣Ž║─╩ăÍŞË╔ø╝■Íđ╦¨Ë𿞡w╣▄Á─đ╣┬ęŰŐ┴¸úĘď┤śOÁŻ┬ęśOĎď╝░ľ┼śOđ╣┬ę,│ú│ú╝»Íđ×ÚýoÍ╣ŰŐ┴¸úęĎřĂÁ─╣Ž║─,Ďď╝░╚╬║╬Ăń╦ű║ŃÂĘ╣Ž║─đŔăˇÍ«║═íúđ╣┬ęŰŐ┴¸║▄┤ˇ│╠Â╚╔¤╚íŤQË┌ŻYťě║═żžˇw╣▄│▀┤šíú

íííí ║ŃÂĘ╣Ž║─đŔăˇ░Ř└ĘϲŻKŻËúĘ╚š╔¤└şŰŐÎŔúę°ďý│╔Á─ŰŐ┴¸đ╣┬ęíúŤ]ËđÂÓ╔┘┤Ű╩ę┐╔Ďď▓╔Ë├üÝË░ÝĹđ╣┬ę,Áź║ŃÂĘ╣Ž║─┐╔ĎďÁ├ÁŻ┐ěÍĂíú

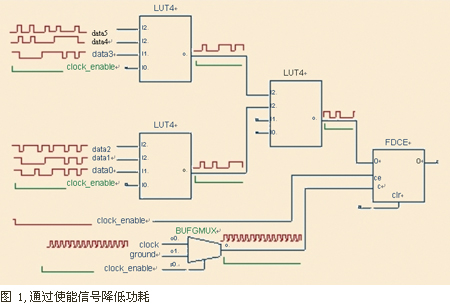

▒Mďš┐╝Ĺ]╣Ž║─

íííí ─˙ď┌ďOËőÁ─ďšĂ┌ŰAÂ╬Î÷│÷Á─╣Ž║─ŤQÂĘË░ÝĹÎţ┤ˇíúŤQÂĘ▓╔Ë├╩▓├┤ď¬╝■îŽ╣Ž║─ż▀ËđÍě┤ˇĎÔ┴x,°ď┌ĽršŐ╔¤▓ň╚ŰĎ╗éÇ BUFGMUX ätË░ÝĹ╔§╬óíúîŽ╣Ž║─Á─┐╝Ĺ]ďŻďšďŻ║├íú

ăí«öÁ─ď¬╝■

íííí ▓ó▓╗╩ă╦¨Ëđď¬╝■Â╝ż▀Ëđ¤Ó═ČÁ─ýoÍ╣╣Ž║─íúިô■ĂŇ▒ÚĎÄät,ø╝■╣Ą╦ç╝╝đg│▀┤šďŻđí,đ╣┬ę╣Ž║─ďŻ┤ˇíúÁź▓ó▓╗╩ă╦¨Ëđ╣Ą╦ç╝╝đgÂ╝Ď╗śËíú└ř╚š,îŽË┌ 90 nm ╝╝đgüÝŇf,Virtex-4 ø╝■┼cĂń╦ű 90 nm FPGA ╝╝đgÍ«Úgď┌ýoÍ╣╣Ž║─ĚŻ├Š┤Šď┌´@Í°▓ţ«É,

íííí ╚╗°,ď┌ýoÍ╣╣Ž║─ŰS╣Ą╦ç╝╝đg┐sđí°ď÷╝ËÁ─═ČĽr,äËĹB╣Ž║─ůsŰSÍ«ťpđí,▀@╩ăË╔Ë┌Ţ^đíÁ─╣Ą╦çËđÍ°ŞŘÁ═Á─ŰŐë║║═ŰŐ╚Ţíú┐╝Ĺ]║├──ĚN╣Ž║─îŽ─ŃÁ─ďOËőË░ÝĹŞŘ┤ˇí¬í¬┤řÖCúĘýoÍ╣úę╣Ž║─▀Ç╩ăäËĹB╣Ž║─íú

íííí │ř═ĘË├ăđĂČ▀ëŢőć╬ď¬═Ô,╦¨ËđXilinxø╝■Â╝ż▀ËđîúÚT▀ëŢőíúĂńđ╬╩ŻËđëK RAMíó18í┴18 │╦ĚĘøíóDSP48 ëKíóSRL16s,Ďď╝░Ăń╦ű▀ëŢőíú▀@▓╗âHď┌Ë┌îúÚT▀ëŢőż▀ËđŞŘŞ▀Á─đď─▄,▀Çď┌Ë┌╦Řéâż▀ËđŞŘÁ═Á─├▄Â╚,ϲ°îŽË┌¤Ó═ČÁ─▓┘θ┐╔Ďď¤ű║─Ţ^╔┘Á─╣Ž┬╩íúďu╣└─˙Á─ø╝■▀xÝŚĽr,Ňł┐╝Ĺ]îúÚT▀ëŢőÁ─ţÉđ═║═öÁ┴┐íú

íííí ▀xô˝▀m«öÁ─ I/O ś╦ť╩Ď▓┐╔Ďď╣Ł╩í╣Ž║─íú▀@đęÂ╝╩ă║ćć╬Á─ŤQÂĘ,╚š▀xô˝ÎţÁ═Á─˛îäËĆŐÂ╚╗˛Ţ^Á═Á─ŰŐë║ś╦ť╩íú«ö¤ÁŻy╦┘Â╚Ϭăˇ╩╣Ë├Ş▀╣Ž┬╩ I/O ś╦ť╩Ľr,ËőäŁĎ╗éÇ╚▒╩íáţĹBĎďŻÁÁ═╣Ž║─íúËđÁ─ I/O ś╦ť╩úĘ╚š GTL/+úęđŔϬ╩╣Ë├Ď╗éÇ╔¤└şŰŐÎŔ▓┼─▄Ňř│ú╣ĄÎ¸íúϲ┤╦╚š╣űďô I/O Á─╚▒╩íáţĹB×ÚŞ▀ŰŐï°▓╗╩ăÁ═ŰŐĂŻ,ż═┐╔Ďď╣Ł╩í═Ę▀^ďôŻKŻËŰŐÎŔÁ─Í▒┴¸╣Ž║─íúîŽË┌ GTL+,îó50ŽŞŻKŻËŰŐÎŔÁ─▀m«ö╚▒╩íáţĹBďOÍ├×Ú 1.5V,┐╔╩╣├┐éÇ I/O ╣Ł╩í╣Ž║─ 30 mAíú

öÁô■╩╣─▄

íííí «ö┐éżÇ╔¤Á─öÁô■┼c╝─┤ŠĂ¸¤ÓŕPĽr,ŻŤ│ú╩╣Ë├ĂČ▀x╗˛ĽršŐ╩╣─▄▀ëŢőüÝ┐ěÍĂ╝─┤ŠĂ¸Á─╩╣─▄íú▀MĎ╗▓ŻüÝŇf,▒MďšîŽďô▀ëŢő▀Mđđí░öÁô■╩╣─▄í▒,ĎďÎŔÍ╣öÁô■┐éżÇ┼cĽršŐ╩╣─▄╝─┤ŠĂ¸ŻM║¤▀ëŢőÍ«Úg▓╗▒ěϬÁ─ŮDôQ,╚šłD 1 ╦¨╩żíú╝t╔ź▓Ęđ╬▒Ý╩żďşďOËő;żG╔ź▓Ęđ╬▒Ý╩żđŮŞ─║ˇÁ─ďOËőíú

íííí ┴ÝĎ╗ĚN▀xô˝╩ăď┌ŰŐ┬Ě░ň╔¤Â°▓╗╩ăď┌đżĂČ╔¤▀Mđđ▀@ĚNí░öÁô■╩╣─▄í▒íúĎď▒M┐╔─▄ťpđí╠Ä└ÝøĽršŐÍ▄Ă┌íú┤╦Ş┼─ţ╩ă╩╣Ë├ CPLD Ć─╠Ä└ÝøđÂŢd║ćć╬╚╬äŇ,Ďď▒Ń╩╣ĂńŞŘÚLĽrÚgÁě╠ÄË┌┤řÖC─ú╩Żíú

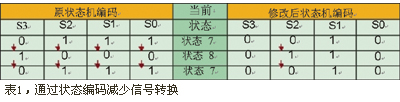

íííí Îî╬ĎéâüÝ┐┤Ď╗éÇď┌áţĹB 7 ║═áţĹB 8 Í«ÚgţlĚ▒▀MđđáţĹBŮDôQÁ─áţĹBÖCíú╚š╣ű─˙×ÚďôáţĹBÖC▀xô˝Â■▀MÍĂżÄ┤a,îóĎÔ╬ÂÍ°îŽË┌├┐┤╬áţĹB 7 ║═áţĹB 8 Í«ÚgÁ─áţĹBŮDôQ,îóËđ╦─╬╗đŔϬŞ─ÎâáţĹB,╚š▒Ý 1 ╦¨╩żíú╚š╣űáţĹBÖC▓╔Ë├Ş˝└Î┤a°▓╗╩ăÂ■▀MÍĂ┤aüÝďOËő,ät▀@â╔éÇáţĹBÍ«ÚgÁ─ŮDĎĂ╦¨đŔÁ─▀ëŢőŮDôQÁ─öÁ┴┐îóŻÁÍ┴âHĎ╗╬╗íú┴Ý═Ô,╚š╣űîóáţĹB 7 ║═ 8 ĚÍäeżÄ┤a×Ú 0010 ║═ 0011,Ď▓┐╔Ďď▀_ÁŻ═ČśËÁ─đž╣űíú

ĽršŐ╣▄└Ý

íííí ď┌Ď╗éÇďOËőÁ─╦¨Ëđ╬Ř╩Ň╣Ž║─Á─đ┼╠ľ«öÍđ,ĽršŐ╩ăδ┐řÁť╩ÎíúŰm╚╗Ď╗éÇĽršŐ┐╔─▄▀\đđď┌ 100 MHz,ÁźĆ─ďôĽršŐ┼╔╔˙│÷Á─đ┼╠ľůs═Ę│ú▀\đđď┌͸ĽršŐţl┬╩Á─Ţ^đíĚÍ┴┐úĘ═Ę│ú×Ú 12% ~ 15%úęíú┤╦═Ô,ĽršŐÁ─╔╚│÷Ď╗░ŃĎ▓▒╚Ţ^Ş▀í¬í¬▀@â╔éÇϲ╦ě´@╩ż,×Ú┴╦ŻÁÁ═╣Ž║─,Ŭ«öŇJŇŠĐđż┐ĽršŐíú

íííí ╚š╣űďOËőÁ──│éÇ▓┐ĚÍ┐╔Ďď╠ÄË┌Ěă╗ţäËáţĹB,ät┐╔Ďď┐╝Ĺ]╩╣Ë├Ď╗éÇ BUFG-MUX üÝŻűÍ╣ĽršŐśńĚşŮD,°▓╗╩ă╩╣Ë├ĽršŐ╩╣─▄íúĽršŐ╩╣─▄îóÎŔÍ╣╝─┤ŠĂ¸▀Mđđ▓╗▒ěϬÁ─ĚşŮD,ÁźĽršŐśń╚ď╚╗Ľ■ĚşŮD,¤ű║─╣Ž┬╩íú▓╗▀^▓╔Ë├ĽršŐ╩╣─▄┐é▒╚╩▓├┤┤Ű╩ęĎ▓Ť]ËđĆŐíú

íííí Ş˘ŰxĽršŐĎď╩╣Ë├Îţ╔┘öÁ┴┐Á─đ┼╠ľů^íú▓╗╩╣Ë├Á─ĽršŐśńđ┼╠ľů^▓╗Ľ■ĚşŮD,Ć─°ŻÁÁ═ďôĽršŐżWŻjÁ─ěôŢdíúÎđ╝Ü▓╝żÍ┐╔Ďďď┌▓╗Ë░ÝĹîŹŰHďOËőÁ─ăÚŤr¤┬▀_ÁŻ┤╦─┐ś╦íú

íííí îŽ FPGA ´@╚╗Ď▓┐╔Ďď╩╣Ë├═ČĎ╗Ş┼─ţíúŰm╚╗ FPGA ▓╗Ď╗ÂĘôÝËđ┤řÖC─ú╩Ż,Áź╩╣Ë├Ď╗éÇ CPLD Íđ═żÖ┌Żě┐éżÇöÁô■▓óËđ▀xô˝ÁěîóöÁô■ü╦═ÁŻ FPGA Ď▓┐╔Ďď╩í╚ą▓╗▒ěϬÁ─Ţö╚ŰŮDôQíú

íííí CoolRunner-II CPLD ░Ř║ČĎ╗ĚNĚQ×Úí░öÁô■ÚT┐ěí▒Á─╣Ž─▄,┐╔ĎďŻűÍ╣Ďř─_╔¤Á─▀ëŢőŮDôQÁŻ▀_ CPLD Á─â╚▓┐▀ëŢőíúďôöÁô■ÚT┐ě╩╣─▄┐╔═Ę▀^ĂČ╔¤▀ëŢő╗˛Ďř─_üÝ┐ěÍĂíú

áţĹBÖCďOËő

íííí Ş¨ô■ţAťyÁ─¤┬Ď╗áţĹBŚl╝■┴đ┼eáţĹBÖC,▓ó▀xô˝│úĹBÍ«ÚgŮDôQ╬╗Ţ^╔┘Á─áţĹBÍÁíú▀@śË,─˙ż═─▄ë˛▒M┐╔─▄ťp╔┘áţĹBÖCżWŻjÁ─ŮDôQ┴┐úĘţl┬╩úęíú┤_ÂĘ│úĹBŮDôQ║═▀xô˝▀m«öÁ─áţĹBÍÁ,╩ăŻÁÁ═╣Ž║─ăĎîŽďOËőË░ÝĹŢ^đíÁ─Ď╗ĚN║ćć╬ĚŻĚĘíúżÄ┤ađ╬╩ŻďŻ║ćć╬úĘĎ╗╬╗ËđđžżÄ┤a╗˛Ş˝└Î┤aúę,╩╣Ë├Á─ŻÔ┤a▀ëŢőĎ▓Ľ■ďŻ╔┘íú

íí╣Ž║─╣└╦Ń╣Ąż▀

íííí ┘Éý`╦╝╠ß╣ę┴╦â╔ĚNđ╬╩ŻÁ─╣Ž║─╣└╦Ń╣Ąż▀ú║Ď╗ĚNŻđÎ÷ Web Power Tools Á─ďOËőă░╣Ąż▀║═Ď╗ĚNŻđÎ÷ Xpower Á─ďOËő║ˇ╣Ąż▀íúWeb Power Tools ┐╔═Ę▀^ www.xilinx.com/cn/power ź@Á├,╦Ř╠ß╣ę┴╦ިô■▀ëŢő└űË├┬╩┤ˇŞ┼╣└ËőÎ÷│÷Á─╣Ž║─╣└╦Ńíú└űË├╦Ř,─˙┐╔ĎďâHĹ{ďOËő└űË├┬╩╣└Ëőż═─▄ź@Á├╣Ž║─ďu╣└,°čođŔîŹŰHďOËő╬─╝■íú

íííí XPower ╩ăĎ╗ĚNďOËő║ˇ╣Ąż▀,Ë├Ë┌ĚÍ╬÷îŹŰHø╝■└űË├┬╩,▓óŻY║¤îŹŰHÁ─▀m┼ń║ˇ (post-fit) Ě┬ŇŠöÁô■úĘVCD ╬─╝■Ş˝╩Żúę,Żo│÷îŹŰH╣Ž║─öÁô■íú└űË├ Xpower,─˙┐╔Ďďď┌═ŕ╚ź▓╗ŻËË|đżĂČÁ─ăÚŤr¤┬ĚÍ╬÷ďOËőŞ─ÎâîŽ┐é╣Ž║─Á─Ë░ÝĹíú

╗¨Ë┌ Web Á─╣Ž║─╣Ąż▀

íííí ╗¨Ë┌ Web Á─╣Ž║─╣└Ëő╩ăď┌ďOËő┴¸│╠Á─ďšĂ┌ź@Á├ø╝■╣Ž║─ăÚŤrÁ─Îţ┐ýŻŢ║═ÎţĚŻ▒ŃÁ─ĚŻĚĘíú▀@đę╣Ąż▀├┐éÇ╝żÂ╚Â╝Ľ■░l▓╝đ┬░Š▒ż,ϲ┤╦đ┼¤ó┐é╩ăÎţđ┬Á─,ăĎ▓╗đŔϬ░▓Đb╗˛¤┬Ţd,Í╗đŔϬôÝËđ╗ą┬ôżW▀BŻË║═ Web ×gË[ø╝┤┐╔íú─˙┐╔ĎďÍŞÂĘďOËőůóöÁ▓ó▒ú┤Š║═╝ËŢdďOËőďOÍ├,├Ô╚ą┴╦═Ę▀^Ż╗╗ą╩╣Ë├Íěđ┬Ţö╚ŰďOËőůóöÁÁ─┬ÚčęíúÍ╗ϬËđîŽďOËőđđ×ÚÁ─╣└Ëő▓ó▀xÂĘ─┐ś╦ø╝■╝┤┐╔Ú_╩╝íú

Xpowerú║╝»│╔Á─ďOËőîúË├╣Ž║─ĚÍ╬÷

íííí Xpower ╩ă╦¨Ëđ Xilinx ISEďOËő╣Ąż▀Á─Ď╗éÇ├Ô┘MŻM╝■,─˙┐╔Ďď└űË├╦ŘîŽ─˙Á─╗¨Ë┌ďOËőÁ─╣Ž║─đŔăˇ▀Mđđďö╝ÜÁ├ÂÓÁ─╣└ËőíúXPower ╩ăď┌Ë│╔ń╗˛▓╝żÍ║═▓╝żÇ║ˇďOËőÁ─╗¨ÁA╔¤îŽĂ¸╝■╣Ž║─▀Mđđ╣└ËőÁ─íú

íííí îŽË┌│╔╩ýÁ─═«aÁ─ FPGA ║═ CPLD,XPower Ëő╦Ń│÷Á─╣Ž║─╣└ËőÁ─ĂŻż¨ďOËő┼˙┴┐Ň`▓ţ (suite error) đíË┌ 10%íú╦Řîó░Đø╝■öÁô■┼c─˙Á─ďOËő╬─╝■ŻY║¤ĂüÝżC║¤┐╝Ĺ],▓ó░┤ŇŇ─˙Á─îúÚTďOËőđ┼¤óŻo│÷╣└Ëőø╝■╣Ž║─Á─Ş▀żźÂ╚łˇŞŠíú

íííí XPowerÍ▒ŻË╝»│╔ď┌ ISE ▄Ť╝■Íđ,┐╔╠ß╣ęîË┤╬╗»Á─ďö╝ÜÁ─╣Ž║─´@╩żíóďö╝ÜÁ─┐éŻYłˇŞŠ║═╣Ž║─¤˛îž,╝┤╩╣╩ăđ┬Ë├ŢĎ▓┐╔ŢpĎÎ╔¤╩ÍíúXPower ┐╔ŻË╩▄Ě┬ŇŠÁ─ďOËő╗ţäËöÁô■,▓ó┐╔Ďď GUI ─ú╩Ż║═┼˙╠Ä└Ý─ú╩Ż▀\đđíú

íííí XPower îó┐╝Ĺ]ďOËőÍđÁ─├┐éÇżWŻj║═▀ëŢőď¬╦ěíúISE ďOËő╬─╝■╠ß╣ęť╩┤_Á─┘Yď┤╩╣Ë├ăÚŤr;XPower Ż╗▓Šůó┐╝▓╝żÇđ┼¤óĎď╝░╠ěđď╗»ŰŐ╚ŢöÁô■íúË┌╩ă╬´└Ý┘Yď┤ßśîŽŰŐ╚Ţ▀Mđđ╠ěđď╗»íúďOËő╠ěđď╗»îóîŽđ┬ø╝■│Í└m▀Mđđ,ĎďŻo│÷Îţżź┤_Á─ŻY╣űíúXpower ╩╣Ë├┴╦żWŻjĚşŮD╦┘┬╩║═Ţö│÷ěôŢdíú╚╗║ˇ XPower Ëő╦Ń╣Ž║─║═ŻYťě,▀Ç┐╔Ďď´@╩żć╬éÇżWŻjÁ─╣Ž║─öÁô■íú

ŻYŇô

íííí Ř▒ŃĎ╦║═ŞŘ║ćć╬Á─čß╣▄└ÝĎď╝░┼că░Đě FPGA ▓╗öÓ╠ߪ▀Á─╣Ž║─đŔ㡤ÓĂą┼ńÁ─ŰŐď┤Á─▓╗öÓď÷ÚLÁ─đŔăˇ,îóÁ═╣Ž║─ďOËőÁ─Ş┼─ţ╠ß╔řÁŻĎ╗éÇ╚źđ┬Á─Ş▀Â╚íú┘Éý`╦╝Îţđ┬ø╝■ Virtex-4 FPGA ╠ß╣ę┴╦ 90 nm ╣Ą╦ç╝╝đgÁ─Ş▀đď─▄,ůs▒▄├Ô┴╦ţA¤ŰÍđýoĹB╣Ž║─Á─´@Í°ď÷┤ˇíú╩╣Ë├┘Éý`╦╝╣Ž║─╣└╦Ń╣Ąż▀▓óνкÁ═╣Ž║─ďOËő┐╝Ĺ]╩┬ÝŚ,ŁMÎŃ─˙Á─╣Ž║──┐ś╦îó▒╚Ďď═¨╚╬║╬Ľr║˛Â╝ŞŘ╝Ë╚ŢĎÎíú

]]>╣Ž─▄╠ěŘcú║

1íóÍž│ÍXilinx╣ź╦żÁ─FPGAďOËőú╗

2íó▓╔Ë├Spartan3Á─╝Š╚ŢďOËőúČđżĂČ×Úú║XC3S400PQ208ú╗

3íó░ň╔¤ŰŐď┤ú║5Víó1.2Víó2.5V;

4íóPQ208ĚÔĐbúČŁMÎŃÂÓIO ďOËőđŔăˇ;

5íóÍž│ÍXilinxÁ─JTGAď┌żÇ┼ńÍ├Ň{ďç;

6íóÍž│ÍXCF02SđżĂČ┼ńÍ├║═│╠đ˛╣╠╗»;

7íó4╬╗7Â╬öÁ┤a╣▄;

8íó8éÇ░┤ŠIŢö╚Ű;

9íó8éÇ░l╣ÔÂ■śO╣▄;

10íóś╦ť╩RS232┤«đđŻË┐┌;

11íóPS2╩ˇś╦íóŠI▒PŻË┐┌;

12íóϢţlŢö│÷ŻË┐┌;

13íóĚń°QøŢö│÷ŻË┐┌;

14íóVGAĎĽţlŻË┐┌;

15íóÍž│ÍI2CđżĂČAT24CXX¤Á┴đđżĂČÁ─ÎxîĹ;

16íóÍž│Í1602Ď║żž´@╩ż

17íóÍž│ÍÄžŁhÎÍÄýÁ─12864Á─Ď║żž´@╩ż(╚šOCMJ48);

18íó256 K16bit SRAM, ┐╔Ďďθ×ÚäËĹB┤ŠâŽđżĂČ;

19íó32╬╗SDRAM(┐╔▀_128M), ŁMÎŃ┤ˇ╚Ţ┴┐đŔăˇ▀MđđSOPC│╠đ˛┤ŠâŽ;

20íó50MżžŇ˝, ┐╔Ďďâ╚▓┐▒ÂţlŁMÎŃŞ▀╦┘ďOËőđŔăˇ;

21íóżžŇ˝┐╔▓ň░╬, ŞŘŞ─×ÚĂń╦űţl┬╩.

╣Ô▒Pâ╚╚Ţ╝░Ňf├¸ú║

1) íóÚćÎxø Acrobat Reader 6.0

2) íóöÁô■╩Íâď FPGAđżĂČöÁô■╩Íâď,Ďď╝░═Ôç˙đżĂČ(╚šflashsdramsramlcdÁ╚)Á─öÁô■╩Íâď

3) íó░▓ĐbÍŞ─¤ ise░▓ĐbÍŞ─¤

4) íó▄Ť╝■Ż╠│╠ ║ć├¸Íđ╬─Ż╠│╠

5) íóŇ{ďç╣Ąż▀ ťyďç╣Ąż▀úČ░Ř║Č┤«┐┌═Ęđ┼ťyďç│╠đ˛

6) íóďş└ÝłD Ú_░l░ňďş└ÝłD

7) íóø╝■▀xđ═ xilinx«aĂĚ▄ŤË▓╝■▀xđ═ÍŞ─¤

8) íóŰŐď┤▀xđ═ xilinx«aĂĚŰŐď┤▀xđ═ÍŞ─¤

9) íóË├Ţ╩Íâď Ë├Ţ╩ÍâďúČŇłË├Acrobat Reader×gË[

10) íóexamples Ú_░l░ň└řÎË(░Ř║Č╣Ą│╠ďOËő║═╬─ÖnŇf├¸,║ČPS2 MouseKeyboardVGARS232LCDLEDSOPCÁ╚)

11) íó▄Ť╝■▓┐ĚÍ(software) ise_6.3╗˛ise_web.

╣Ô▒P╦¨ÄžÁ─└řÎË│╠đ˛

sw_demo░┤ŠIťyďç│╠đ˛;seg_demo 7Â╬öÁ┤a╣▄ĽršŐ´@╩ż│╠đ˛;imageshowĆ─SRAMÍđÎx╚íöÁô■▓ó´@╩ż│╠đ˛;

lcd_demoĎ║żž─úëK´@╩ż│╠đ˛(128x64ÄžŁhÎÍÄý);led_demo░l╣ÔÂ■śO╣▄´@╩ż│╠đ˛;

mouse_seg╩ˇś╦ĎĂäË▓ó´@╩żď┌7Â╬öÁ┤a╣▄╔¤│╠đ˛;uart_demo RS232┤«đđ═Ęđ┼│╠đ˛,╩╣Ë├┤«┐┌Í˙╩ÍŻË╩Ň░l╦═öÁô■;

vga_demo▓╩Ślđ┼╠ľ´@╩ż│╠đ˛;music_demoϢţl░l╔˙øúČ═ÔŻËϢ¤ń╝┤┐╔Ë├░┤ŠIĐŢÎÓ│╠đ˛;sram_demoÎxîĹsram│╠đ˛;

lcd_demo_1602Ď║żž1602Á─ÎxîĹ´@╩ż│╠đ˛;edk_led╩╣Ë├ăÂ╚Ű╩Żâ╚║╦┐ěÍĂled│╠đ˛;

edk_uart╩╣Ë├ăÂ╚Ű╩Żâ╚║╦┐ěÍĂ┤«┐┌│╠đ˛;edk_sdram╩╣Ë├ăÂ╚Ű╩Żâ╚║╦ťyďçsdram│╠đ˛;^-^Ăń╦ű└řÎË▓╗öÓŞŘđ┬Íđ.

ŞŘÂÓ«aĂĚđ┼¤óúČÜgËşÁăńŤżWŇż╗˛ŰŐďĺ▓Úďâíú

]]>

Ě└┐ŻěÉ╝╝đgĎ▓▓╗ňeíú

1.▒ż┘|ŻYśő▓╗Ď╗śË

ííííACTEL╩ă╗¨Ë┌flashŻYśőúČALTETAíóXINLINX(┘É┴Í╦╝)║═LatticeÂ╝╩ă▓╔Ë├SRAMŻYśőúČÁ˘ŰŐöÁô■üG╩ž,╦¨ĎďđŔϬĎ╗ëK┼ńÍ├đżĂČúČ°ACTELčoÝÜ┼ńÍ├íú

íííí2.░▓╚źđď-čoĚĘĂĂŻÔ

ííííACTEL FPGAâ╚▓┐Ëđ2Íě▒ú├▄╣Ž─▄ú║Ď╗éÇ╩ă128╬╗Flashlock╝Ë├▄úČĎ╗éÇ╩ă128╬╗Á─AESÁ─╝Ë├▄(╚ź▓┐ď┌▄Ť╝■└´├ŠÎďË╔ďOÍ├)úČŇŠŇř▀_ÁŻ▒úÎo─˙Á─ͬÎR«aÖÓíúFlashlock├▄ŔÇ╩ă▒úÎođżĂČúČĚ└Í╣╦ű╚╦▀Mđđđž˛×íóżÄ│╠íó▓┴│říúÍ╗ËđŇř┤_Á─128╬╗Flashlock├▄ŔÇ▓┼─▄▀MđđîŽđżĂČ▓┴│řÍěîĹíú2Á─64┤╬ĚŻĎĐŻŤ║▄┤ˇ┴╦úČ2Á─128┤╬ĚŻż═ŞŘ┤ˇ┴╦íúż═╦Ń▀\ÜÔ║├úČ░ĐFlashlock├▄┤aĂĂŻÔ┴╦úČÁź│╠đ˛┤˙┤aËÍ╩ă╩╣Ë├128╬╗Á─AES╝Ë├▄íú╚š╣űË├╩└Żš╔¤Îţ┐ýÁ─Ëő╦ŃÖCĎ▓Ϭ1░┘â|─ŕíú╦¨ĎďACTELÁ─┤˙┤a╗¨▒ż┐╔ĎďîŹČFżW╔¤é¸ŢöúČż═╦Ń╚╦╝ĎŻě┴╦Ď▓Ť]ËđË├íúĎ▓ďSËđ╚╦Ľ■ŇfË├Ě┤¤˛╣Ą│╠úČ▓╔╚í─ąđżĂČź@╚íÚ_ŕPáţĹBíúÁź╩ăACTELÁ─żžˇw╣▄Â╝ď┌7îËŻî┘Ń~Í«¤┬úČ╚š╣ű░Đă░7îËŻî┘╚ąÁ˘┴╦úČ▀Ç▓╗ĂĂë─▓╝żÇŻYśő║═â╚▓┐żžˇw╣▄úČ▀@╗¨▒ż╩ă▓╗┐╔─▄Á─úČ▀@Ď▓╩ă▄Ő╩┬║═║Ż┐ŇÍđ╚ź▓┐╩╣Ë├ACTELÁ─ďşĎ˛íú

íííí3.╔¤ŰŐ╝┤▀\đđ

ííííACTEL┼cĂń╦ű╣ź╦żÁ─FPGA¤Ó▒╚Á─┴ÝĎ╗éÇâ×Řcż═╩ă╔¤ŰŐ╝┤▀\đđíú▀@éÇ╠ěđďËđÍ˙Ë┌¤ÁŻyŻM╝■Á─│§╩╝╗»íó╠Ä└ÝøćżđĐżo╝▒╚╬äŇÁ─ł╠đđúČ°ALTERAíóXINLINXÁ─FPGA╔¤ŰŐÁŻŇř│ú╣ĄÎ¸đŔϬ0.2├ŰÁ─ĽrÚgíú▀@Ď╗ŘcĎ▓Ňř╩ăACTELĆVĚ║Ë├Ë┌║Ż┐Ň╗˛Ň▀▄Ő╩┬ţI˲Á─ďşĎ˛íú└ř╚šú║ď┌▓╗═ú▄ç╩Ň┘M¤ÁŻyÍđúČż═└űË├┴╦ACTELÁ─╔¤ŰŐż═▀\đđíúĂű▄çď┌Ş▀╦┘╣ź┬Ě╔¤đđ╩╣Á─╦┘Â╚╠ěäe┐ý,°ď┌▀hŰx╩Ň┘M¤ÁŻyÍđ,FPGA╩ă╠ÄË┌Á˘ŰŐáţĹB.«öŻËŻŘ╩Ň┘Mů^Á─Ľr║˛,FPGAćóäË╣ĄÎ¸,╦¨ĎďďOËőÍđ▒ěÝÜϬŁMÎŃFPGA╔¤ŰŐż═╣ĄÎ¸,SRAMđ═Á─FPGA╔¤ŰŐ┼ńÍ├Ϭ200MS,ËđŘc▓╗═Î,┐╔─▄îžÍ┬ŻY╣ű╩ă:Á╚ÁŻFPGAÚ_╩╝╣ĄÎ¸Á─Ľr║˛,▄çĎĐŻŤÚ_│÷┴╦╔ńţlů^,▄çŢd░l╦═Á─öÁô■͸ҿčoĚĘ╩ŇÁŻíú

íííí4.ŇŠŇřÁ─ć╬đżĂČŻÔŤQĚŻ░Ş

ííííACTEL╩ăflash╝▄śőÁ─FPGAúČ°ALTERA║═XINLINXÁ─Â╝╩ăSRAM╝▄śőúČÁ˘ŰŐöÁô■üG╩žúČ╦¨ĎďĎ╗░ŃđŔϬ═Ô╝ËĎ╗éÇ┼ńÍ├đżĂČíúË╔Ë┌ACTEL╩ăflash╝▄śőÁ─FPGAúČ╦¨Ďď▓╗Ϭ┼ńÍ├đżĂČúČ°ăĎ╣Ž║─ŞŘÁ═íúACTELÁ─FUSION¤Á┴đŞŘ╩ăâ╚▓┐Äž─úöM╣Ž─▄,â╚▓┐ËđŰŐ┴¸▒O┐ěúČŰŐë║▒O┐ěúČ12╬╗ADúČRTCÁ˘ŰŐćżđĐÁ╚Á╚.IGOOL¤Á┴đŞŘ╩ă×Ú╩Í│ÍďOéń┴┐╔ÝÂĘÎ÷úČýoĹB╣Ž║─×Ú5╬ó═▀úČÎţđíĚÔĐbâH×Ú4mm*4mm,▒╚śIŻšÎţÁ═╣Ž║─Á─CPLD╣Ł╩í500▒ÂĎď╔¤íú

íííí5.čo┐╔╠˘╠ŮÁ─ĚÇÂĘđď

ííííACTELż▀Ëđ╣╠╝■├ÔĎ▀─▄┴ŽúČż═╩ă╚╬║╬Ş▀─▄┴┐Á─ÍđÎË║═a┴úÎËÎ▓ô˘Ă¸╝■Â╝Żz║┴Ť]ËđË░ÝĹúČÁź╩ăSRAMđ═Á─FPGA╩ă▓╗─▄│đ╩▄Ş▀─▄┴┐┴úÎËÁ─Î▓ô˘úČ▓╗─▄▀m║¤É║┴ËÁ─şhż│íú─┐ă░╔¤║úÍđ┐Ăď║╬´└ÝĐđż┐╦¨│đô˙Á─"Š¤Â1╠ľ"ÝŚ─┐ÍđúČż═╩ă╩╣Ë├Á─ACTEL¤Á┴đĚ┤╚█Żz¤Á┴đÁ─đżĂČíú▀@éÇĎ▓╩ăACTELď┌▄Ő╩┬íóĂű▄çđđśIÍđÁ─â×äŢ╦¨ď┌íú

íííí6.═ŕŇű├Ô┘MÁ─Ú_░lĂŻ┼_

íííí▄Ť╝■═ŕ╚ź├Ô┘MúČâ╚▓┐╝»│╔┴╦śIŻšÎţ║├Á─żC║¤╣Ąż▀synplifyúČĚ┬ŇŠÎţ║├Á─╣Ąż▀MODESIMÁ╚úČ▓╗╩Ň╚í╚╬║╬┘MË├úČ╚ź▓┐ÎďäË═ŕ│╔░▓ĐbúČ▄Ť╝■Ú_░l║ćć╬úČ╩╣Ë├ĚŻ▒Ńíú╬ĎéâËđĎ╗¤Á┴đďö╝ÜÁ─└ř│╠(PLL,RAM,FIFO,Flashrom,äËĹBPLL),Îî─˙Ţp╦╔îŹČF┤˙┤aÁ─ĎĂÍ▓íú═ČĽrÎţđ┬Á─2▒żACTELĽ°╝«(ACTELďş└Ý┼cŬË├║═ACTEL×└ř│╠úę║═▒ŃĎ╦Á─Ú_░l░ňÎî─˙Ď╗éÇđăĂ┌ż═┐╔Ďď═ŕ╚źŇĂ╬ŇACTELďOËőÁ─żź╦Ŕíú

íííí7.ACTELâ╚▓┐░Ř║ČARM7╗˛CORTEX_M1╠Ä└Ýø

ííííÄžM7║═M1ă░żYÁ─FPGAÂ╝Íž│ÍARM╠Ä└ÝøúČĎ▓ż═╩ăFPGAâ╚▓┐▓╗ć╬┐╔ĎďîŹČFFPGAÁ─╣Ž─▄úČ▀ÇËđARM╠Ä└ÝøúČîŹČFí░FPGA+ARMí▒Á─ŻM║¤ĚŻ░Ş,ż═¤ˇALTETA└´├ŠÁ─NIOS IIíú

íííí8.═ŕ╚ź╠Š┤˙śIŻšÁ─CPLDø╝■

ííííACTEL FPGAôÝËđ3-300╚fÚTÍ«ÚgÁ─ø╝■úČď┌═ČÁ╚ârŞ˝ÍđúČ╬Ďéâ▓╗Áźż▀éńCPLD╚ź▓┐Á─╣Ž─▄úČ▀Çż▀éńPLLúČRAMúČFIFOúČ1KÁ─flashROMúČ128╬╗Á─AES├▄ŔÇúČŻ^îŽÁ─┐╔┐┐đďíú▀@śËÁ─ďĺúČ╬Ďéâ▀ÇËđ╩▓├┤└ÝË╔▓╗▀xË├ACTELíú

▒ż╚╦▓╗╩ăACTELÁ─┤˙└ÝúČĎď╔¤Ň¬ÎďEDN.

Ě└┐ŻěÉŰm╚╗▓╗└űË┌╝╝đgŻ╗┴¸úČîŽË┌áśI┐╔╩ă╔˙╦└┤Š╗ţÁ─╩┬ăÚúȤÓđ┼▀Ç╩ăËđ╩đł÷Á─íú]]>

íííí×Ú┴╦ď┌ŞéáÄÍđŇ╝ô■͸äËúČPLD╩đł÷äŢż¨┴Žö│Á─â╔┤ˇţIîžĆS╔╠Xilinx┼cAlterađ┬ŻŘĚÍäeđű▓╝╦űéâÁ─¤┬Ď╗┤˙FPGA«aĂĚÂ╝îó▓╔Ë├Ş▀kŻî┘ľ┼╝╝đgÁ─28nm╣Ą╦çúČĎďŁMÎŃÍT╚šďĂËő╦ŃíóĎĂäË╗ą┬ôżW║═3GŬË├Á╚ţI˲╦¨▓╗öÓď÷ÚLÁ─ÄžîĺđŔăˇíúϲ×ÚPLDø╝■▓╔Ë├ŞŘŞ▀╝╝đgÁ─╣Ą╦ç╣ŁŘcÍĂďýúČčoĎ╔┐╔ĎďŻÁÁ═│╔▒żíó╠ß╔řđď─▄úČË╚Ăń╩ă─▄벪─▀MĎ╗Í▒ĎďüÝ×ÚASIC╦¨ďŹ▓íÁ─╣Ž║─╦«ĂŻúČĎď▀mŬŞŘĆVÚčÁ─ďOËőŬË├íú╚╗°PLDŰpđ█«öă░ż¨╬┤ďö╝Ü═Ş┬ÂŞ¸Îď28nm╝╝đgÁ─«aĂĚĎÄäŁúČ╣└ËőϬÁ╚ÁŻŻ˝─ŕQ3ĚŻ┐╔═ŕ╚źŻĎĽďíú

íííí╩Ô═ż═ČÜwÁ─╩ăúČAltera║═XilinxÂ╝ĆŐŇ{ď┌28nm╝╝đg╔¤Á─▓┐ĚÍ┐╔Íěđ┬┼ńÍ├╣Ž─▄úČ╝┤FPGAø╝■čođŔöÓŰŐż═┐╔Ďď═Ę▀^▄Ť╝■îŽĂńâ╚▓┐▀ëŢő▀Mđđ▓┐ĚÍÍěÍ├íú▓╗═ČÁ─╩ăúČXilinxđűĚQĂńď┌ďô╣Ž─▄Á─Íž│Í╔¤ŞŘË𯍲×úČ▓óŞ´├ŘđďÁěŻyĎ╗Virtex║═Spartanø╝■Á─â╚▓┐▀ëŢő║═I/O╝▄śőüÝ╠ß╣ęý`╗ţÁ─ďOËő▀xô˝ú╗°AlteraÁ─28nmø╝■╠ěŘcät╩ăď┘ŻY║¤ăÂ╚Ű╩ŻHardCopy─úëK║═ŞŘŞ▀╦┘Á─╩Ň░løüÝ▀f╦═ŞŘŞ▀Á─đď─▄íú

íííí28nmø╝■┤˙╣ĄĚŻ├ŠúČAlteraĎ└╚╗Í╗Ë╔ĂńÚLĂ┌Ĺ┬ď╗´░Ú┼_ĚeŰŐ(TSMC)┤˙╣ĄúČ°łď│ÍÂÓ┤˙╣Ą▓▀┬ďÁ─Xilinx│ř▀xô˝ĎĐ╩ă65nm┤˙╣Ą╗´░ÚÁ─╚řđă═ÔúČĎ▓ŮD°═Â╚ŰTSMCÁ─ĹĐ▒žíúô■¤ĄúČ┼_ĚeŰŐ(TSMC)ĎĐŻŤť╩éń║├ď┌─ŕâ╚ďç«aŞ▀kŻî┘ľ┼28nmø╝■íú▒ż┐»═ČĽrŇJ×ÚúČ║═┤˙╣ĄĆSÁ─▓ęŮ─îóĽ■╩ăŤQÂĘFPGAŰpđ█ź@╚í28nm╩đł÷ŞéáÄ╗I┤aÂÓ╔┘Á─Ď╗éÇÍěϬϲ╦ěúČ▒╚╚šď┌┴┐«aĽrÚgíó«a─▄Íž│ÍÁ╚Ş¸ĚŻ├ŠíúŇ\╚╗úČ╝Ą┴ĎÁ─╩đł÷ŞéáÄ╩ă═ĂäË28nm FPGA─╦Í┴╝Ë╦┘PLD«aśI░lŇ╣Á─ď┤╚¬úČ°äôđ┬Á─28nm FPGAø╝■Á─═Ă│÷úČîŽË├ŢüÝŇfčoŇô╚š║╬Â╝╩ă║├╩┬Ď╗╝■úČ°▓╗╣▄──éÇ╣ęŬ╔╠ď┌ÎţŻKÁ─╩đł÷╔¤▒ÝČFŞŘä┘îŽĚŻĎ╗╗Iíú

íííí─▄┘xËŔďOËőŞŘż▀ý`╗ţđďÁ─╠ěŘc╩╣╩đł÷îŽFPGAÁ─đŔăˇĎ▓│╩ČFÂÓśË╗»íúů^äeË┌SRAM FPGAď┌Ş▀Â╦DSP║═żWŻj╠Ä└ÝŬË├╔¤Á─│╔ż═úČ┴ÝĎ╗PLD╣ęŬ╔╠Actelż═ŤQĎÔĎď╗¨Ë┌Flash╝╝đgÁ─Á═╣Ž║─FPGA▀Mđđ▓ţ«É╗»ŞéáÄíúActelüć╠źů^┐鯍└Ý┘çý┼ÍŢîŽíÂŰŐÎË╣Ą│╠îúŢőíĚ▒Ý╩żúČActelÁ─▓▀┬ď╩ăĹ{ŻŔ╗ý║¤đ┼╠ľFPGAäôŻĘî┘Ë┌ActelÎď╝║Á─╩đł÷íú╦űŇJ×ÚúČActelÎţđ┬═Ă│÷╝»│╔ARM Cortex-M3Ë▓║╦║═┐╔żÄ│╠─úöM─úëKÁ─SmartFusion FPGAúČś╦ͿͰ╩Î┐ţ═ŕ╚ź┐╔żÄ│╠Á─SoCÁ─ŇQ╔˙íúď┌Ăń─┐ś╦ŬË├ţI˲└´úČĂń¤Ó▒╚MCU+ASSPÁ─ĚŻ░ŞŻM║¤ż▀ËđŞŘŞ▀Á─╝»│╔Â╚║═ďOËőý`╗ţđďúČ°îŽË┌╗¨Ë┌CMOS╣Ą╦çÁ─SRAM FPGA°ĐďúČ╗¨Ë┌Flash╣Ą╦çÁ─SmartFusionôÝËđŞ▀ë║─úöMŰŐ┬Ě║═öÁÎÍŰŐ┬Ě╣▓┤ŠÁ─â×äŢíú┘çý┼ÍŢŻÚŻBúČFlash FPGAđŔϬŞ▀ŰŐë║čřńŤúČ╚ŢĎÎ╝»│╔─úöM┘Yď┤úČ°SRAM FPGAď┌Ş▀ŰŐë║╝»│╔ĚŻ├Š▒╚Ţ^Ëđ╠˘ĹđďúČĎ╗░ŃüÝŇfúČ3.3VĎď╔¤Á─đ┼╠ľŰyĎď╝»│╔ÁŻSRAM FPGA╔¤íú

ííííSmartFusionÁ─äôđ┬üÝÎďĂńăÂ╚Ű┴╦═ŕŇűÁ─╬ó┐ěÍĂøÎˤÁŻyúČĎ▓╩ă┼că░┤˙╝»│╔▄Ť║╦Á─Fusion«aĂĚÁ─ů^äe╦¨ď┌íú┐╔żÄ│╠─úöMĚŻ├ŠúČĂń͸Ϭż▀ËđÄÎéÇ12╬╗SAR ADC║═Sigma-Delta DAC┐╔▀xô˝íú°▄Ť╝■Íž│ÍĚŻ├ŠúČ║═┤ˇÂÓöÁăÂ╚Ű╩ŻÚ_░l╠Î╝■Á─â╚╚Ţ▓ţ▓╗ÂÓúČÁźĂń╬ó┐ěÍĂøÎˤÁŻyÁ─┼ńÍ├╣Ąż▀Á─┤_╩ăĎ╗éÇ┴┴ŘcúČďOËő╚╦ćTÍ╗đŔ╣┤▀x¤ÓŬÁ─═ÔďO║═I/O┼cŢö╚ŰË▓╝■┼ńÍ├╝┤┐╔úČ°┐╔żÄ│╠─úöMď¬╝■Ď▓┐╔═Ę▀^Ş─╣Ąż▀▀Mđđ┼ńÍ├íú

íííí┘çý┼ÍŢĆŐŇ{úČď┌SmartFusion═Ă│÷▓╗ż├╦¨ôÝËđÁ─╩«ÂÓéÇ┐═ŢüÝ┐┤úČ▀xô˝Actel FPGAÁ─ŕPŠI▀Ç╩ăĂń╠ěËđÁ─▒ú├▄đď╠ěŘcíúË╔Ë┌Actel Flash FPGA╩ăone die╝»│╔úČ═ÔĺýŻË┐┌Ţ^╔┘úČ╝Ë╔¤ÂÓîË┤╬Á─▒úÎo┤Ű╩ęúČ─▄ËđđžĚ└Í╣äôđ┬Á─╗˛▓ţ«É╗»ďOËő▒╗ŞéáÄîŽ╩Í│şĎuíó┐╦┬íúČ╔§Í┴▒╗┤˙╣ĄĆS╔╠▀^┴┐╔˙«aíú

]]>╚š╣ű─▄ď┌FPGAâ╚▓┐ăÂ╚Űż▀Ëđ═Ô▓┐ťyďçďOéń╣Ž─▄Á─▀ëŢőťyďç─úëKúČ─ă├┤Ďď╔¤ćľţ}ż═┐╔ĎďĎ╗Ď╗ŻÔŤQíúSignalTapIIż═╩ă▀@śËĎ╗ĚNăÂ╚Ű╩Ż▀ëŢőĚÍ╬÷ø(embedded logicanaIyzer)úČ║ćĚQ×ÚSignalTapII ELAíú╦Ř╩ăQuartusII▄Ť╝■Íđ╝»│╔Á─â╚▓┐▀ëŢőĚÍ╬÷▄Ť╝■úČ╩╣Ë├╦Ř┐╔ĎďrË^▓ýâ╚▓┐đ┼╠ľ▓Ęđ╬úČĚŻ▒ŃË├Ţ▓ÚŇĎďOËőÁ─╚▒¤Ţíú

1 SignalTapII ELAÁ─ďş└Ý

SignalTapII ELA╩ăQuartus▄Ť╝■ÍđÁ┌Â■┤˙¤ÁŻy╝ëŇ{ďç╣Ąż▀íúîóSignalTapII ELA┤˙┤a║═¤ÁŻy▀ëŢő┤˙┤aŻM║¤Ż╗Ë╔QuartusIIżÄÎgíóżC║¤íó▓╝żÍ▓╝żÇúČ╔˙│╔sol╬─╝■Íđâ╚║ČSignalTapII ELAúČ░Đsof╬─╝■┼ńÍ├ÁŻFPGAâ╚íúFPGA▀\đđĽrúČĎ╗ÁęŁMÎŃ┤řťyđ┼╠ľÁ─Ë|░lŚl╝■úČSignalTapII ELAż═┴ó╝┤ćóäËúČ░┤ŇŇ▓╔śËĽršŐÁ─ţl┬╩▓Âź@┤řťyđ┼╠ľöÁô■▓óĽ║┤ŠË┌FPGAĂČâ╚Á─RAMÍđúČ▓╔śËöÁô■▓╗öÓ╦óđ┬ĂČâ╚┤ŠâŽĂ¸úČÎţ║ˇ═Ę▀^JTAG┐┌îó▓Âź@Á─đ┼╠ľĆ─ĂČâ╚RAMé¸Í┴Quartus IIr´@╩żíúSignalTapII ELAÁ─ďş└Ý┴¸│╠╚šłD1╦¨╩żíú

îŹŰH╣Ą│╠ÍđúČ╝Ë╚ŰSignalTapII ELA▓╗Ľ■Ë░ÝŤÁŻyďşËđÁ─▀ëŢő╣Ž─▄íú

2 SignalTapII ELAÁ─┼ńÍ├

SignalTapII ELA╗¨▒ż┼ńÍ├▀^│╠╚š¤┬ú║

ó┘╠Ý╝Ë▓╔śËĽršŐíúSignalTaplI ELAď┌ĽršŐÁ─╔¤╔řĐě▀Mđđ▓╔śËúČ┐╔Ďď╩╣Ë├ďOËő¤ÁŻyÍđÁ─╚╬║╬đ┼╠ľÎ¸×Ú▓╔śËĽršŐúČŞ¨ô■Altera╣ź╦żÁ─ŻĘÎhÎţ║├╩╣Ë├═Č▓Ż¤ÁŻy╚źżÍĽršŐθ×Ú▓╔śËĽršŐíúÁź╩ăď┌îŹŰHŬË├ÍđúČÂÓöÁ╩╣Ë├¬Ü┴óÁ─▓╔śËĽršŐúČ▀@śË─▄▓╔śËÁŻ▒╗ťy¤ÁŻyÍđÁ─┬ř╦┘đ┼╠ľúČ╗˛┼c╣ĄÎ¸ĽršŐ¤ÓŕPÁ─đ┼╠ľíú«ö╚╗▓╔śËĽršŐÁ─ţl┬╩Ϭ┤ˇË┌▒╗ťyđ┼╠ľÁ─ÎţŞ▀ţl┬╩úČĚ˝ät▒╗ťyđ┼╠ľ▓Ęđ╬Ľ■ËđŢ^┤ˇŇ`▓ţíú

ó┌ÂĘ┴x▓╔śË╔ţÂ╚íú▓╔śË╔ţÂ╚ŤQÂĘ┴╦┤řťyđ┼╠ľ▓╔śË┤ŠâŽÁ─┤ˇđíúČ°┐╔Ďď▓╔śËÁ─╔ţÂ╚╩㪨ô■ďOËőÍđ╩úËÓÁ─RAMëK╚Ţ┴┐║═┤řťyđ┼╠ľÁ─éÇöÁŤQÂĘÁ─íú╚˘┤řťyđ┼╠ľŢ^ÂÓúČätď┌═ČśËIú»O BankéÇöÁăÚŤr¤┬▓╔śË╔ţÂ╚Ţ^ť\íú┤řťyđ┼╠ľéÇöÁÁ─ď÷ťp║═▓╔śË╔ţÂ╚Á─╔ţť\Ľ■Í▒ŻËŞ─ÎâRAMëKÁ─Ň╝Ë├ăÚŤrúČ▓╔śË╔ţÂ╚Á─ĚÂç˙×Ú0íź128 KBíú

ó█ÂĘ┴xRAMţÉđ═íúďOÍ├Ň╝Ë├ĂČâ╚║╬ĚNRAMëK┘Yď┤úČŰSÍ°▓╔śË╔ţÂ╚Á─Ş─ÎâúČRAMëKÁ─öÁô■żÇ║═ÁěÍĚżÇîĺÂ╚┐╔ĎďĚÍŞţ│╔ÂÓĚNŻM║¤íú└ř╚šú║▓╔śË╔ţÂ╚╩ă1 KBúČRAMöÁô■żÇíóÁěÍĚżÇ┐╔ĎďĚÍŞţ│╔2í┴512╗˛4í┴256Á╚ÂÓĚNŻM║¤íúĎ└┤╦ţÉ═Ăíú

ó▄ÂĘ┴xË|░l╬╗Í├íúPre trigger position▒Ý╩ż▓╔śËÁŻÁ─öÁô■12úą×ÚË|░lă░úČ88úą×ÚË|░l║ˇú╗Center trigger position▒Ý╩ż▓╔śËÁ─öÁô■╠ÄË┌Ë|░lă░║ˇŞ¸Ď╗░Űú╗Post trigger position▒Ý╩ż▓╔śËÁŻÁ─öÁô■88úą×ÚË|░lă░úČ12úą×ÚË|░l║ˇíú

óŢË|░lŚl╝■╝ëöÁďOÍ├íúSignalTapII ELAÍž│ÍÂÓË|░l╝ëÁ─Ë|░lĚŻ╩ŻúČÎţÂÓ┐╔Íž│Í10╝ëË|░lúČÄ═Í˙×V│ř▓╗¤ÓŞ╔Á─öÁô■úČŞŘ┐ýÁěŇĎÁŻđŔϬÁ─öÁô■íú╚˘ËđÂÓ╝ëË|░lŚl╝■úČ╩Τ╚ĚÍ╬÷Á┌Ď╗╝ëË|░lŚl╝■íú╚˘Á┌Ď╗╝ë×ÚTRUEúČätŮDÁŻĚÍ╬÷Á┌Â■╝ë╩ăĚ˝ŁMÎŃúČÍ▒ÁŻĚÍ╬÷═ŕ╦¨ËđË|░lŚl╝■ż¨×ÚTRUE▓┼ÎţŻKË|░lĽršŐ▓╔śËöÁô■íú

óŮË|░lŚl╝■íúďOÂĘ╝s╩°đďÁ─Ë|░lŚl╝■íú┐╔Ďďď╩ďSć╬éÇđ┼╠ľÁ─¬Ü┴óË|░lŚl╝■BasicúČÍ▒ŻË▓╔Ë├ć╬éÇ═Ô▓┐╗˛ďOËő─úëKâ╚▓┐Á─đ┼╠ľú╗Ď▓┐╔Ďďď╩ďSÂÓéÇ╣ŁŘcđ┼╠ľÁ─ŻM║¤Ë|░lŚl╝■AdvancedúČśő│╔Ë|░l║»öÁÁ─Ë|░lŚl╝■ĚŻ│╠íú└ř╚šú║╩╣─▄đ┼╠ľENA┼c4╬╗Ţö│÷đ┼╠ľQ¤Ó┼c║ˇË|░lúČË|░lŚl╝■=ENA&(Q=15)íú

]]>

ŰSÍ°ŰŐÎËď¬╝■Á─đď─▄║═╝»│╔Â╚▓╗öÓ╠ߪ▀°ârŞ˝ůs▓╗öÓŻÁÁ═úČŰŐÎË┐ěÍĂć╬ď¬Á─░lŇ╣ŇřĎ╗╚Ňăž└´íúŰSͰ޸ĚN╝╝đg║═ŬË├┤ˇ┴┐Ë┐ČFúČĆ─╝ĎŰŐţI˲ÁŻ╣ĄśIÎďäË╗»╔˙«ażÇúČ┤ˇ╝ĎŕPÎóÁ─ÍěŘc▀Ç╩ăď┌ď÷╝ËďOËő║═╠ߪ▀ŰŐď┤đž┬╩Á─═ČĽr─▄ťp╔┘ďOËőíóÚ_░l║═ŇűˇwÁ─¤ÁŻy│╔▒żíú

íííí

┼c┤╦═ČĽrúČ▀\äË┐ěÍĂŬË├Á─Ć═Űs│╠Â╚Ď▓ďŻüÝﯪ▀úČĎĐĆ─║ćć╬Á─Ú_/ŕPđ═┐ěÍä˛ď┌Ş▀Â╚╝»│╔şhż│Íđż▀éńżź┤_┐ěÍĂÁ─┐╔Îâ╦┘ŬË├░lŇ╣íúčoŇô╩ăŻ╗┴¸íóÍ▒┴¸íóËđ╦ó║═čo╦óŰŐÖCÁ─޸ĚN┐ěÍĂŰŐ┬Ě͸ϬË╔╚ř▓┐ĚÍśő│╔ú║╚╦ÖCŻš├Šíó╬ó┐ěÍĂøúĘMCUúę ║═┐ěÍĂ▀ëŢőíúîŽË┌Ú]şh▀\äË┐ěÍĂúČ鸪đøŻË┐┌╩ă═Ô╝ËÁ─Ď╗éÇď¬╝■úĘłD1úęíúîó▀\äË┐ěÍĂ▀ëŢő╝{╚ŰöÁÎÍţI˲┐╔ĎďîŹČFĚÍ▓╝╩Żşhż│┐ěÍĂíú▀\äË┐ěÍĂŰŐÎË║═ĚÍ▓╝żWŻjÁ─┼ń║¤┐╔ď┌▄çÚgîŹČFÂÓĚNđ┬╣Ž─▄úČ░Ř└Ę▀h│╠╣▄└Ýú╗▀mŬ▓╗öÓÎâ╗»Á─ůfÎhú╗đď─▄▒OĎĽú╗Ďď╝░░┤Ă┌▀MđđżSÎoíú

┼e└řŇfúČ«öŻ˝Ăű▄çÍĂďýśIĆVĚ║╩╣Ë├Ë╔▓Ż▀MŰŐÖC˛îäËÁ─ÖCđÁ╩ÍíúÖCđÁ╩ͤÁŻy╩╣Á├ĚÍ▓╝╩Ż┐ěÍĂŞŘ×ÚĆ═ŰsúČ°▓╗═ČÁ─ÖCđÁ╩ÍϬ═ČĽrď┌ÄÎéÇ▄çŢv╔¤░▓Đb▓╗═ČÁ─┴Ń╝■íú¤ÁŻyďOËő╚╦ćT͸ϬÁ─╠˘ĹÍ«Ď╗╩ăϬ═Ę▀^żÍ˲żW

ŻjîŹČF޸éÇÖCđÁ╩Í║═Ăń╦űÎďäË╗»ďOéńÁ─═Č▓ŻíúŞŘĆ═ŰsÁ─╩ăúČ▀h│╠╣▄└Ý╣Ž─▄úĘ╚š▒OĎĽíóöÁô■╣▓¤Ý║═▀h│╠┼ńÍ├úę îŽĆ═ŰsÁ─ÍđĐŰ┐ěÍĂ═ěôńŻYśő═¨═¨Ěă│úŕPŠIúČĎ▓ż═╩ăŇfúČ▒ěđŔËđĎ╗éÇËđđžÁ─ĚÍ▓╝┐ěÍĂÖCÍĂíú

íííí

ŰSÍ°░Űw╣Ą╦ç║═╝»│╔Â╚Á─╠ߪ▀úČČFł÷┐╔żÄ│╠ÚTŕç┴đúĘFPGAúę ĎĐ│╔×ÚďSÂÓŰŐÎË▀\äË┐ěÍĂŬË├Á─ÍěϬ╠Š┤˙ĂŻ┼_íúFPGAÁ─░lŇ╣ĐŞ├═úČď┌ďSÂÓŬË├ţI˲Íđ╠Š┤˙┴╦╠ěÂĘË├═ż╝»│╔ŰŐ┬ĚúĘASICúęíúĚăĎÎ╩žđďFPGA╩ăż▀│╔▒żđžĎŠÁ─ASIC╠Š┤˙ĚŻ░ŞúČ▓╗┤Šď┌▓╔Ë├ASICĽr╔Š╝░Ú_░l│╔▒żŞ▀║═Ú_░lĽrÚgÚLÁ─ćľţ}íú°ăĎúČ└űË├FPGA╠Š┤˙╣╠ÂĘÁ─▀ëŢőúČďOËő╚╦ćTčoŇôď┌ďOËőŰAÂ╬▀Ç╩ăď┌ŬË├ČFł÷úČÂ╝┐╔ĎďŞ▀đžíó┐╔┐┐ÁěîŹČF«aĂĚ╔ř╝ë╝░ÂĘÍĂ╣Ž─▄íú

íííí

ĎďFlash ×Ú╗¨ÁAÁ─╗ý║¤đ┼╠ľFPGA úĘ╚šActel Fusion PSCúę ─▄ď┌ć╬đżĂČ╔¤îŹČFă░╦¨╬┤ËđÁ─╝»│╔Â╚íúϲ┤╦úČ▀@ţÉø╝■┐╔╠Š┤˙ÂÓéÇĚÍ┴óď¬╝■úČ─▄╩╣│╔▒ż║═Ň╝Ë├░ň┐Ę┐ŇÚgťp╔┘Îţ╔┘50%úČ═ČĽrËÍ─▄żS│ͤÁŻyÁ─┐╔┐┐đďúĘłD2úęíú°ăĎúČ╗ý║¤đ┼╠ľĂ¸╝■╔¤╝»│╔Á─Flash â╚┤Š┐╔ĎďÎîďOËő╚╦ćT┤ŠâŽďOËő╬─ÖnúČ▓╗¤ˇ─ăđęĎďSRAM×Ú╗¨ÁAÁ─FPGAđŔϬ┴Ý═Ô┼ńÍ├PROMíú┤╦═ÔúČ┼cĂń╦ű┐╔ÍěżÄ│╠FPGAŻÔŤQĚŻ░ŞĎ╗śËúČ┐╔┼ńÍ├║═ý`╗ţÁ─╗ý║¤đ┼╠ľFPGAø╝■┐╔Ďďď┌Ú_░l▀^│╠Íđ╔§Í┴ŬË├Í«║ˇúČŢpĎÎ▀MđđďOËőÎâŞŘíú

íííí

▒Ő╦¨Í▄ͬúČFPGA─▄═Ę▀^▓óđđ╠Ä└Ý╝Ë┐ýöÁîW▀\╦ŃúČ╩╣╦Ř│╔×ÚîŹČFŰŐÖC┐ěÍĂ▀ëŢőÁ─└ݤŰ▀xô˝íúFPGA─▄ł╠đđŞŘç└Ş˝Á─┐ěÍĂşhúČϲ┤╦╠ß╣ęŞŘ╝ĐÁ─┐ěÍĂ║═ŞŘ╔┘Á─▓ĘäË║═ďŰ┬ĽíúďOËő╚╦ćT▀Ç─▄ď┌╝»│╔┴╦Flash â╚┤ŠÁ─╗ý║¤đ┼╠ľFPGAÍđ╝»│╔▄Ť╠Ä└Ýø║╦úČĆ─ĂČ╔¤┤ŠâŽĂ¸Í▒ŻË▀\đđúČĆ─°żo├▄Áě┼ń║¤┐ěÍĂ▀ëŢő║═ÍđöÓ˛îäË│╠đ˛Á─đŔϬíúË╔Ë┌ďOËőÍđÁ─▀ëŢőÚTöÁ┴┐║═ţÉđ═╝░┐ěÍĂ▀ëŢőÁ─╣Ž─▄ϲŬË├°Ëđ╦¨▓╗═ČúČ╝┤╗¨Ë┌đď─▄ϬăˇÂ°ÂĘú╗ϲ┤╦úČ┐╔żÄ│╠▀ëŢő═¨═¨Îţ▀m║¤Ë┌îŹČF޸ĚNË├ŢŻË┐┌║═öÁÎÍ┐ěÍĂ▀ëŢőúČ░Ř└ĘżWŻj║══ÔďOŻË┐┌íó├}Ť_îĺÂ╚Ň{ÍĂúĘPWMúęúČĎď╝░ŇřŻ╗żÄ┤aøŻË┐┌║═鸪đøŢö╚Űú╗▀@öŻ˝Á─▀\äË┐ěÍäÁŻyÂ╝Ěă│úÍěϬíú

íííí

żWŻj║══ÔďOŻË┐┌

íííí

ď┌▀\äË┐ěÍäÁŻyÍđúČżWŻj║══ÔďOŻË┐┌┐╔ÎîË├Ţ░l│÷ÍŞ┴ţîŽ▀ëŢőŰŐ┬Ě▀Mđđ│§╩╝╗»íó┼ńÍ├║═┐ěÍĂúČ▓óăĎ▀h│╠╣▄└Ý┐ěÍäÁŻyíúިô■╣Ž─▄║══ěôńŻYśőÁ─▓╗═ČúČ├┐éÇ▀\äË┐ěÍäÁŻyÁ─żWŻj║══ÔďOŻË┐┌Â╝┐╔─▄Ľ■▓╔╚í¬Ü╠ěÁ─îŹČFĚŻ╩ŻúČÁźËđĎ╗Řc╣▓═ČÁ─╩ăúČÂ╝Ľ■└űË├ŻË┐┌üÝ╠ߪ▀¤ÁŻyÁ─┐╔ďLćľđďíú

íííí

─┐ă░ĎĐŻŤËđ޸ĚN޸śËÁ─╣ĄśIś╦ť╩ŻË┐┌úČ╚šË├Ë┌▒żÁěďLćľÁ─═ĘË├┤«đđ┐éżÇúĘUSBúęíó╗¨Ë┌RS232Á─┤«┐┌║═┐ěÍĂøżÍ˲żWúĘCANúę ŻË┐┌úČĎď╝░╗¨Ë┌TCP/IPżWŻjůfÎhÁ─10/100Ďď╠źżWíúď┌┐┴┐╠Á─şhż│¤┬úČ╚šĂű▄çÍĂďý▄çÚgúČ┐╔─▄▀ÇđŔϬčożÇżWŻjŻË┐┌íú▀@ĚNŻË┐┌┐╔ď┌ÍĂďý▄çÚgâ╚îŹČF¤ÁŻy═Č▓ŻíóöÁô■╣▓¤ÝíóáţĹB▒OĎĽ║═╣╩Ҥłˇż»íú┤╦═ÔúČ╗¨Ë┌TCP/IPÁ─żWŻjŻË┐┌ätË├Ë┌ĐËÚLË╔╚╬║╬żÓŰx▀h│╠ďLćľÍđĐŰÍĂďý┐ěÍĂďO╩ęÁ──▄┴Žíú

ď┌ďSÂÓăÚŤr¤┬úČ╣ĄśIÎďäË╗»Ĺ¬Ë├Â╝đŔϬ╠ě╩ÔÁ─┐ěÍĂ╦ŃĚĘ║═ĐbÍ├üÝ═ŕ│╔╠ě╩ÔÁ─╚╬äŇíú×ÚîŹČF▀@đęś╦ť╩ŻË┐┌čoĚĘ╠ß╣ęÁ─╣Ž─▄úČđŔϬ┐╝Ĺ]▓╔Ë├îúÚTÁ─ŻË┐┌íú×Ú┴╦│ńĚÍ░lô]─│éÇĚÍ▓╝┐ěÍäÁŻyÁ─Łô┴ŽúČś╦ť╩ŻË┐┌╗˛îúÚTÁ─żWŻjůfÎhÂ╝▒ěÝÜ╝ËÁŻ░ň┐Ę╝ëÍđúČ╗˛ăÂ╚ŰÁŻ┐╔żÄ│╠▀ëŢőâ╚íú°FPGA╩ăîó╦¨ËđŻË┐┌╝»│╔ď┌Ď╗ĂÁ─Îţ╝ĐĂŻ┼_íú╠ěäe╩ăúČ«öŻ˝Á─╗ý║¤đ┼╠ľFPGAø╝■ż▀Ëđ─úöMă░Â╦úČ─▄Íž│ÍĚNţÉ▒ŐÂÓÁ─Ë├ŢŢö╚ŰúČĎď╝░îŹČF▀\äË┐ěÍĂ╦¨đŔÁ─ŰŐë║íóŰŐ┴¸║═ťěÂ╚▒OĎĽ╣Ž─▄íú

íííí

├}Ť_îĺÂ╚Ň{ÍĂúĘPWMúę

íííí

PWM▀ëŢő▓ó▓╗╩ă╦¨Ëđ▀\äË┐ěÍĂŬË├Â╝▀mË├Á─ĚŻ░ŞíúË╔Ë┌▓╗═ČŰŐÖCÁ─└@ŻM╚ŽöÁíóţ~ÂĘŰŐë║/ŰŐ┴¸íó┼Ążěă˙żÇ║═Ăń╦űůóöÁÁ─▓ţ«É║▄┤ˇúČϲ┤╦├┐ĚNPWM¤ÁŻyÂ╝đŔϬîŽ▀@đę▓ţ«É╝ËĎď┐╝Ĺ]íúď┌PWM┐ěÍĂÁ─¤ÁŻyÍđúČ╩ę╝ËŰŐë║Á─Ýśđ˛ŤQÂĘŰŐÖCÁ─ŮDäËĚŻ¤˛íúď┌ŻoÂĘ└@ŻMŰŐŞđ¤┬úČŇ╝┐Ň▒╚úĘ╗˛Ň▀Ňf├}Ť_ţl┬╩║═├}Ť_┤«ÚLÂ╚úę ŤQÂĘ┴╦ŰŐÖCÁ─ĚňÍÁŰŐ┴¸║═┤┼═Ę┴┐úĘ╝┤Ăń┼Ążě┤ˇđíúęíúÖCđÁäË┴┐║═└@ŻMŰŐŞđúĘ▓┐ĚÍË╔└@ŻM╚ŽöÁ╦¨ŤQÂĘúę Ľ■╩╣PWMŰŐë║ÎâÁ├ĂŻ╗Číú═Ę▀^┐ěÍòîäËŰŐ┬ĚÁ─╝Ëë║Ýśđ˛íóţl┬╩║═Ň╝┐Ň▒╚úČPWM ¤ÁŻyż═┐╔┐ěÍĂĚŻ¤˛íó╦┘Â╚║═ĂŻż¨┼Ążěíú└űË├FPGA ø╝■úČďOËő╚╦ćT┐╔ĎďśőŻĘÎţ▀m║¤¤ÁŻyϬăˇÁ─PWMĚŻ░ŞúČ°▓╗▒ěĚăÁ├▓╔Ë├鸯yÁ─MCU/DSPĚŻ░ŞüÝîŹČFíú

íííí

ŇřŻ╗żÄ┤aøŻË┐┌úĘQEIúę

íííí

┤ˇÂÓöÁŞ▀żźÂ╚ŰŐÖCúĘ╚šË├Ë┌ÖCđÁ╩ÍÁ─╦┼Ě■▓Ż▀MŰŐÖCúę Â╝Íž│ÍŇřŻ╗żÄ┤aøŻË┐┌íú┐ěÍäÁŻy▒ěđŔ╠ß╣ęŇřŻ╗żÄ┤aøŻË┐┌▀ëŢőüÝżź┤_ŰŐÖC╦┘Â╚íó╬╗Í├║═╝Ë╦┘íú«ö╚╗úČ▓╔Ë├┐╔żÄ│╠▀ëŢő╝╝đg▒Ń┐╔ď┌޸ĚN─ú╩Ż¤┬╚íŤQË┌▀\äË┐ěÍäÁŻyÍđ▓╔Ë├Á─ŰŐÖC╠ěđďúČżź┤_▓óäËĹBÁěŇ{╣Ł╦┘Â╚íú

íííí

鸪đøŢö╚Ű

íííí

îŽË┌Ú]şh▀\äË┐ěÍäÁŻyúČđŔϬËđŮDÎË╬╗Í├║═/╗˛ŮDöÁŢö╚Űíú▀@đęŢö╚Ű┐╔Ďď╩ăâ╚Í├Á─╗˘Â˙đžĹ¬é¸Şđø╗˛═ÔŻËÁ─╣ÔîW╬╗Í├żÄ┤aøíó═Č▓ŻŻÔ╬÷ø╗˛┤┼ŞđŬ鸪đøíú└űË├╝»│╔Á──úöMă░Â╦úČ╗ý║¤đ┼╠ľFPGAîó╠ß╣ęŞŘ╝Ë╝»│╔Á─ŻÔŤQĚŻ░ŞúČ─▄벝p╔┘▓┐╝■öÁíóŻÁÁ═¤ÁŻy│╔▒ż║═╠ߪ▀┐╔┐┐đďíú

íííí

┐╔┐┐đď║═¤ÁŻyŇř│ú▀\đđĽrÚg

íííí

îŽË┌Ż˝╠ýÁ─ŰŐÎˤÁŻyúČŞ▀đď─▄íóÁ═╝»│╔│╔▒ż║═┐ý╦┘ď\öÓ─▄┴ŽĚă│úŕPŠIíúď\öÓ║═ţAłˇúČ╝┤┤_ÂĘ╣╩ҤţÉđ═▓óθ│÷ţAłˇÁ─╣Ž─▄úČď┌¤ÁŻy╣▄└ÝÍđÁ─ÍěϬđďďŻüÝﯪ▀íúÎx╚íÄžËđĽrÚgś╦ËŤ¤ÁŻyůóöÁÁ─޸ĚN░ň┐Ę▀\đđÁ─╣Ž─▄╗˛╩┬║ˇĚÍ╬÷╣╩ҤÁ─╣Ž─▄îŽË┌¤ÁŻyÚ_░l╩ăčoârÍ«îÜíú═ČśËÁěúČ─▄śőŻĘ│÷Ď╗éÇ"║┌¤╗ÎË"îó×Ú▓ÚŇĎ╣╩ҤţÉđ═║═ďOËő╚▒¤Ţ╣Ł╩íîÜ┘FÁ─ĽrÚg║═żź┴Žíú

íííí

╗ý║¤đ┼╠ľFPGAÁ─ĂČ╔¤Flash â╚┤Š┐╔▒ú┤ŠŕPŠIÁ─¤ÁŻyůóöÁúČ▓óîŽĂńθĽrÚgś╦ËŤúČ╚šŰŐď┤żÇ┬ĚŰŐ┴¸¤ű║─íóø╝■ťěÂ╚║═ŰŐë║▓ĘäËÁ╚íú▀@đęöÁô■▓╗âH┐╔Ë├Ë┌╩┬║ˇ╣╩ҤĚÍ╬÷úČ°ăĎ▀Ç┐╔Îîäôđ┬Á─ďOËő╚╦ćTË├Ë┌▀\đđÍđÁ─¤ÁŻy┌ůäŢĚÍ╬÷íú└ř╚šúČďOËő╚╦ćT┐╔Ďďťy┴┐úĘ«öŢö╚Ű─│Ď╗ŰŐë║Ľrúę └@ŻMÁ─ŰŐ┴¸║═ŰŐÖCÁ─Ň˝äËúČĎď┤_ÂĘ╩▓├┤ăÚŤr¤┬░┤ËőäŁÁ─ĚŻ╩ŻŕPÚ]ďOéńíúď┌╣ĄśIŬË├ÍđúČĆ─ŻÔŤQ╣╩Ҥćľţ}╦¨đŔÁ─│╔▒żĎď╝░ďOéńŕPÚ]╦¨ďý│╔Á─└űŁÖôp╩žüÝ┐╝Ĺ]úČ░┤ËőäŁÁ─ĚŻ░ŞŕPÚ]ďOéń▒╚ĎÔ═ÔŕPÚ]Á─┘MË├Ϭ╔┘Á├ÂÓíú╗ý║¤đ┼╠ľFPGA┐╔ÎîďOËő╚╦ćT═Ę▀^ĚÍ╬÷─│Ď╗╠ěÂĘůóöÁ╚š║╬Ş─Îâ░ň┐ĘÁ─ë█├ŘúČď┌╣╩Ҥ░l╔˙ă░θ│÷ţAłˇúČĆ─°Îţ┤ˇ¤ŮÂ╚Áě╠ߪ▀ÖCø└űË├┬╩úČĐËÚL¤ÁŻyÁ─Ňř│ú▀\đđĽrÚgúČ▓óŻÁÁ═┐╔─▄ďý│╔Íě┤ˇôp╩žÁ─¤ÁŻy▒└Łó´LŰUíú

íííí

ŰŐÖCÁ─ŬË├ĚÂç˙║▄ĆVúČ°ăĎďSÂÓŬË├Â╝Ňřď┌Ë╔ÖCŰŐďOËőŮD¤˛ŰŐÎËďOËőíúËő╦ŃÖC║═╣Ž┬╩ŰŐÎËø╝■Á─│╔▒żĎ╗Í▒╩ă═ĂĆVŰŐÎËŰŐÖC┐ěÍĂĆVĚ║ŬË├Á─ҤÁKÍ«Ď╗íúŰSÍ°░Űw╣Ą╦ç║═╣Ž─▄╝»│╔╝╝đgÁ─▀M▓ŻúČ▀@éÇҤÁKŇřď┌┬ř┬ř¤ű╩žíú°ăĎúČË╔Ë┌Ż˝╠ý▓╔Ë├╣╠ÂĘ╣Ž─▄îŹČFĚŻ╩ŻÁ─│╔▒ż╚ď╚╗║▄Ş▀úČ│ú│úđŔϬ▓╗═ČÁ─▓┐╝■║═ď┌޸éÇďOËőĚ┤Ć═şh╣ŁÎ¸░ň┐Ę╝ëÎâŞŘúČFPGA╦ý│╔×Ú┴╦ďSÂÓ▀\äË┐ěÍĂŬË├Á─╠Š┤˙ŻÔŤQĚŻ░Şíú

íííí

└ݤŰÁ─▀\äË┐ěÍĂďOËő═¨═¨đŔϬîóĎ╗đę┐╔ůf═Č▓┘θÁ─▓┐╝■Ě┼ď┌Ď╗ĂúČ╩╣╦Řéâ─▄ď┌▀\đđÍđ║═ÍC┼ń║¤íú°╗ý║¤đ┼╠ľFPGAŻÔŤQĚŻ░ŞÁ─╣Ž─▄╝»│╔Â╚Ěă│úŞ▀úČŇř║├─▄ŁMÎŃ▀@ĚNđŔăˇúČ┐╔Ďď┤ˇĚ¨ťp╔┘▓┐╝■öÁ─┐íó░ň┐Ę┐ŇÚg║═Ňűˇw¤ÁŻy│╔▒żúČĆ─°ď÷╝ˤÁŻyÁ─┐╔┐┐đď║═Ňř│ú▀\đđĽrÚgíú

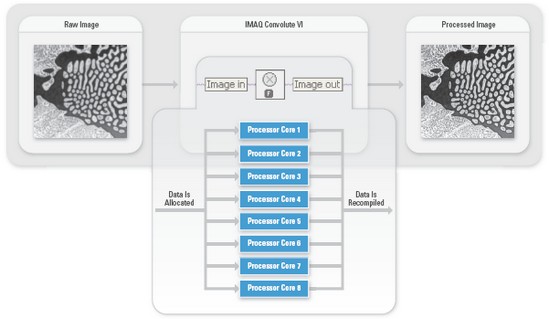

¤Ó╦ĂÁ─úČ─˙ČFď┌äôŻĘÁ─ťy┴┐┼c┐ěÍäÁŻyĎ▓┐╔Ďď═ČĽr▀MđđÂÓÝŚ╚╬äŇíúËő╦ŃţI˲Á─╣Ą│╠äôđ┬Ďř▀M┴╦ďSÂÓŻĘ┴óŞŘŞ▀đž▓óđđ¤ÁŻy╦¨đŔÁ─ŕPŠI╝╝đgú║ÂÓ║╦╠Ä└ÝøíóČFł÷┐╔żÄ│╠ÚTŕç┴đúĘFPGAúę║═čożÇ═Ęđ┼íú╩╣Ë├▀@đę鸯y╣Ąż▀└űË├▀@đęŕPŠI╝╝đg▓ó▓╗╩«ĚÍ╚ŢĎÎú╗Áź╩ăúČ╚š╣űď┌ŬË├Íđ╩╣Ë├▀@đę╝╝đgúČż═┐╔Ďďź@Á├đď─▄ŞŘŞ▀Á─¤ÁŻyúČ╠ߪ▀ťy┴┐┼cÎďäË╗»¤ÁŻyÁ─═╠═┬┴┐úČŻÁÁ═│╔▒żíúLabVIEWÁ─Îţđ┬░Š▒ż8.6×Ú─˙╠ß╣ę┴╦╩╣Ë├¤┬Ď╗┤˙▓óđđ╝╝đg╦¨đŔÁ─╣Ąż▀úČĆ─ÂÓ║╦╠Ä└ÝøÁŻŞ▀đď─▄FPGAÍ▒Í┴čożÇďOéńíú

łD1ú║NIÖCøϼËXÚ_░l─úëKÁ─└ř╚šłD¤˝żÝĚe║»öÁÁ╚ÂÓéÇłD¤˝╠Ä└Ý║»öÁČFď┌─▄ë˛ÎďäËĚÍ┼ńÁŻÂÓéÇ║╦đ─▀Mđđ╠Ä└Ýíú

ď┌Î└├Š╔¤▀MđđÂÓ║╦│Č╝ëËő╦Ń

ď┌╩└ŻšÎţÝö╝ëÁ─500┼_│Č╝ëËő╦ŃÖCúĘwww.top500.orgúęÁ─Îţđ┬┼┼├űÍđúČËđ77úą╩╣Ë├┴╦ÂÓ║╦╠Ä└Ýø┤ěúČ°ď┌2007─ŕ▀@éÇöÁÎÍÍ╗Ëđ22úąíú▀@đę│Č╝ëËő╦ŃÖC║═─˙ČFď┌PCÍđ╩╣Ë├Á─ÂÓ║╦╠Ä└Ýø╩ă¤Ó═ČÁ─íú«ö╚╗úČϬ│ńĚÍ└űË├▀@đę│Č╝ëËő╦ŃÖCđŔϬżÄîĹîúË├Á─▄Ť╝■íúđĎ▀\Á─╩ăúČLabVIEWÁ─ďOËőż═ĎĐŻŤ┐╝Ĺ]┴╦▓óđđ╠Ä└ÝúČîŽÂÓ╚╬äŇ╠Ä└ÝÁ─Íž│ÍĎĐŻŤÚL▀_10ÂÓ─ŕíú

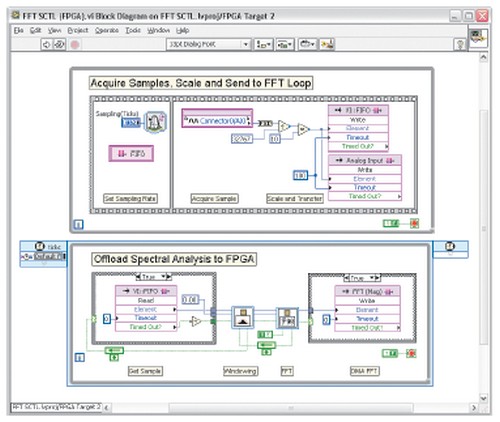

łD2ú║LabVIEW 8.6×ÚFPGAżÄ│╠╠ß╣ę┴╦ĆŐ┤ˇÁ─╦ŃĚĘ╣Ą│╠ĂŻ┼_úČ░Ř║Č┴╦Ż╗╗ą╩ŻË├ŢŻš├Šíó┤ˇđ═ĚÍ╬÷ÄýĎď╝░ÁŻîŹĽrË▓╝■ďşđ═╔¤Á─┐ý╦┘ĎĂÍ▓íú

LabVIEW 8.6╩ă╗¨Ë┌ČFËđÁ─ÂÓ║╦╝Š╚Ţđď°żÄîĹÁ─úČ┤ˇ┤ˇ╠ߪ▀┴╦└űË├ÂÓ║╦╠Ä└Ý╦¨─▄벟@Á├Á─đď─▄íúď┌LabVIEW 8.6Íđ│Č▀^1200éÇöÁîW║═đ┼╠ľ╠Ä└ÝÄýÍđÁ─║»öÁĎĐŻŤ×ÚÂÓ║╦¤ÁŻy▀Mđđ┴╦â×╗»ú╗┤╦═ÔúČđ┬đ═Á─Ş▀╝ëżĆ┤Š▀B└m╝╝đg─▄ë˛▀MĎ╗▓Ż╠ߪ▀đď─▄íú▀@śË╩╣Á├îŽCPU║╦đ─Á─╩╣Ë├ŞŘ×ÚŞ▀đžíú┼e└řüÝŇfúȤÓîŽË┌ć╬║╦¤ÁŻy°ĐďúČĎ╗éÇ▀\đđď┌░╦║╦¤ÁŻy╔¤Á─╗¨ť╩ťyďç│╠đ˛▀\đđ┐ý┴╦6.6▒ÂíúLabVIEW┐ěÍĂďOËő┼cĚ┬ŇŠ─úëKĎ▓╩╣Ë├┴╦ÂÓ║╦╠Ä└ÝøúČł╠đđ▓óđđäËĹB¤ÁŻyĚ┬ŇŠ─úëK┐ý┴╦5▒ÂíúNIÖCøϼËXÚ_░l─úëKÍđÁ─ÂÓéÇłD¤˝╠Ä└Ý║»öÁĎĐŻŤ×ÚÎďäËîó╚╬äŇĂŻĚÍÁŻÂÓéÇ║╦đ─Íđ▀Mđđ┴╦â×╗»íú└ř╚šúČłD¤˝żÝĚe║»öÁÁ─╗¨ť╩ťyďçď┌Űp║╦¤ÁŻy╔¤▀\đđ┐ý┴╦Ş▀▀_15▒ÂúĘĎŐłD1úęíú▀@đęđ┬đ═╠ěđď×Ú─˙Á─ťy┴┐╗˛┐ěÍäÁŻy╠ß╣ę┴╦│Č╝ëËő╦ŃÖC╝ëäeÁ─đď─▄íú

ŻÁÁ═FPGAÚ_░lĽrÚg

FPGA┐╔─▄╩ăČFď┌▓óđđ─▄┴ŽÎţŞ▀Á─┐╔żÄ│╠Ëő╦ŃË▓╝■úČ×Úťy┴┐║═┐ěÍäÁŻy╠ß╣ę┴╦ă░╦¨╬┤ËđÁ─đď─▄║═┐╔┐┐đďíúÁź╩ăúČË╔Ë┌FPGAÁ─Ú_░l└žŰyÍěÍěúČďSÂÓ╣Ą│╠Äč▓╗╠źďŞĎÔ╔ŠÎŃFPGAżÄ│╠íú╔§Í┴╦ŃĚĘďOËőîú╝Ďď┌▀MđđÂĘŘcîŹČFÁ─╣ĄÎ¸Ď▓ËXÁ├╩«ĚÍ└žŰyíúLabVIEW╠ß╣ę┴╦ĆŐ┤ˇÁ─╦ŃĚĘ╣Ą│╠ĂŻ┼_úČ╩╣Ë├Ż╗╗ą╩ŻË├ŢŻš├Šíó┤ˇđ═ĚÍ╬÷Äý║═┼crË▓╝■ďşđ═Á─┐ý╦┘ĎĂÍ▓╠ěđďúČŁMÎŃ┴╦▀@đę╠˘ĹÁ─đŔăˇíúLabVIEW 8.6öUŇ╣┴╦▀@đęŇnţ}úČŻÔŤQ┴╦¤┬├Š┴đ│÷Á─Îţ×Ú│úĎŐÁ─FPGA╠˘Ĺíú

1íó╩╣Ë├鸯yÁ─FPGAÚ_░l▄Ť╝■đŔϬöÁÎÍďOËőÁ─îúśIͬÎRí¬í¬╩╣Ë├LabVIEWÍ▒Ë^Á─öÁô■┴¸─úđ═úČ─˙┐╔Ďď╩╣Ë├łDđ╬╗»LabVIEW FPGA─úëKúČîŽFPGA▀MđđżÄ│╠úČ°▓╗▒ěîW┴ĽË▓╝■├Ŕ╩÷ŇZĐďúĘHDLúęÁ─Ć═Űsâ╚╚Ţíú

2íóFPGA┤˙┤aď┌ł╠đđÍ«ă░┐╔─▄đŔϬ║▄ÚLÁ─żÄÎgÍ▄Ă┌í¬í¬LabVIEW 8.6┤ˇ┤ˇď÷ĆŐ┴╦FPGAÚ_░l║═Ň{ďç╠ěđďúČ─˙┐╔Ďďď┌čođŔżÄÎgÁ─ăÚŤr¤┬úČď┌Ú_░lËő╦ŃÖC╔¤îŽFPGA║═͸ÖCŻË┐┌┤˙┤a▀MđđĚ┬ŇŠíú┤╦═ÔúČČFď┌─˙┐╔Ďďď┌čođŔđŮŞ─FPGA┤˙┤aÁ─ăÚŤr¤┬úČ═Ę▀^Ě┬ŇŠI/Ođ┼╠ľ×ÚFPGA▀ëŢőŻĘ┴óťyďç╣ĄÎ¸┼_úČď┌żÄÎgÍ«ă░îŽďOËő▀Mđđ˛×ÎCíú

╚š╣ű─˙╩╣Ë├NI CompactRIOË▓╝■úČż═┐╔Ďď└űË├LabVIEW 8.6Íđ╚źđ┬Á─CompactRIOĺ▀├Ŕ─ú╩Ż╠ěđďúČčođŔîŽFPGA▀MđđżÄ│╠úČďLćľîŹĽr╠Ä└ÝøÁ─I/OíúËđ┴╦▀@éÇ╚źđ┬▀xÝŚúČď┌─˙Á─ŬË├│╠đ˛đŔϬŞŘŞ▀đď─▄╗˛╩ăÎďÂĘ┴xđđ×ÚĽrúČ┐╔Ďď▀xô˝í░╚ź├ŠÚ_ćóí▒FPGAíú

3íóîó╦ŃĚĘĆ─▄Ť╝■ďşđ═ĎĂÍ▓ÁŻË▓╝■îŹČFÍđ╩«ĚÍ└žŰyí¬í¬Ë╔Ë┌LabVIEW┐╔Ďď▀\đđď┌┼_╩ŻÖCĂŻ┼_║═FPGA╔¤úȤÓîŽË┌╩╣Ë├鸯y╣Ąż▀đŔϬÍěîĹ╦ŃĚĘ°ĐďúČĆ─┼_╩ŻÖCÁŻË▓╝■Á─▀^Â╔╩«ĚÍĂŻ╗ČíúLabVIEW 8.6ÍđFPGA╔¤Á─đ┬ď÷ÂĘŘcöÁô■ţÉđ═Íž│Í║═└ř╚š┐ý╦┘ŞÁ┴ó╚~ÎâôQúĘFFTúę║»öÁÁ╚Ş▀╝ëĚÍ╬÷ͬÎR«aÖÓúĘIPúę╩╣Á├▀@ĚN▀^Â╔ŞŘ╝ËÝś└űíú

4íó╩╣Ë├Îţđ┬Á─FPGAË▓╝■ŞŘđ┬ďOËőđŔϬ║─┘MĽrÚg║═┘YŻí¬í¬LabVIEW═Ę▀^└űË├Ë▓╝■│Ú¤ˇ▒úÎo┴╦─˙Á─Ú_░l═Â┘YúČϲ┤╦─˙┐╔Ďď╩╣Ë├╚źđ┬Ë▓╝■ĂŻ┼_úČ└ř╚š╗¨Ë┌Xilinx Virtex-5 FPGAÁ─NI R¤Á┴đďOéń║═NIć╬░ňRIO░ň┐ĘîúË├┐╔ÍěĆ═┼ńÍ├I/OúĘRIOúęĂŻ┼_úČ°čođŔîŽLabVIEW FPGA┤˙┤a▀MđđđŮŞ─íú

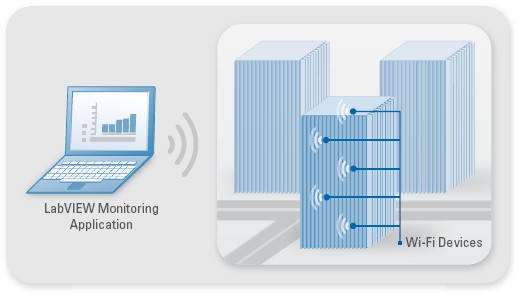

║ć╗»Wi-Fiťy┴┐¤ÁŻyÁ─îŹČF

LabVIEW│ř┴╦║ć╗»┴╦ď┌ÂÓ║╦╠Ä└Ýø║═FPGA╔¤Á─▓óđđ┤˙┤aÚ_░lÍ«═ÔúČ▀Ç═Ę▀^×Úđ┬đ═NI Wi-FiöÁô■▓╔╝»úĘDAQúęďOéń╠ß╣ęÍž│ÍúČ║ć╗»┴╦▓óđđĚÍ▓╝╩Żťy┴┐Á─Ú_░l║═▓┐╩íú▒M╣▄║▄ż├Í«ă░LabVIEWż═ĎĐŻŤ×ÚĎ╗¤Á┴đ▓ň╚Ű╩Ż║═ËđżÇ┐éżÇÁ─öÁô■▓╔╝»╠ß╣ę┴╦Íž│ÍúČ░Ř└ĘPCIíóPXIíóUSBíóLAN║═GPIBúČÁź╩ăď┌öÁô■▓╔╝»Ĺ¬Ë├ÍđčożÇ╝╝đgÁ─Ďř▀Můs┬ř┴╦║▄ÂÓíú▀@͸Ϭ╩ăϲ×ÚîŽ┐╔┐┐íó░▓╚źíóŞ▀đď─▄čożÇ¤ÁŻyÁ─żÄ│╠║═▓┐╩¤ÓŘ×ÚĆ═ŰsíúŰSÍ°Wi-FiúĘIEEE 802.11úęď┌ITţI˲ÍđĂŇ╝░ĎďüÝúČđď─▄íó┐╔┐┐đď║═░▓╚źđďĎĐŻŤ┤ˇ┤ˇ╠ߪ▀┴╦▀@éÇ╝╝đg─▄ë˛▀mË├Ë┌░Ř└ĘöÁô■▓╔╝»ď┌â╚Á─ŕPŠI╚╬äŇÁ─┐╔đđđďíú

îŽ╗¨Ë┌Wi-FiÁ─LabVIEW┼ńÍ├║═öÁô■▓╔╝»▓ŻˇE║═îŽ▒żÁě▓ň╚Ű╩ŻUSBďOéńÁ─đ┼╠ľ▓╔╝»╩ă¤Ó╦ĂÁ─íúâ╔Ň▀Â╝╩╣Ë├¤Ó═ČÁ─LabVIEWŬË├│╠đ˛ŻË┐┌úĘAPIúę▀BŻËNI-DAQmx˛îäË│╠đ˛úČĆ─°▒▄├Ô┴╦ď┌îóWi-FiďOéń╝Ë╚ŰÁŻČFËđËđżÇ╗˛▓ň╚Ű╩ŻNIöÁô■▓╔╝»¤ÁŻyĽr╦¨đŔÁ─┤˙┤ađŮŞ─íúď┌LabVIEWÍđ▀MđđżÄ│╠Á─Ľr║˛úČ─˙┐╔Ďď╩╣Ë├NIöÁô■▓╔╝»Í˙╩ÍúČ▀@╩ăĎ╗éÇ╗¨Ë┌┼ńÍ├Á─¤˛îžúČ─▄ë˛Ä═Í˙─˙ÂĘ┴xťy┴┐úČ┐ý╦┘ĚŻ▒ŃÁě═Ę▀^Wi-Fi▓╔╝»öÁô■íúLabVIEW 8.6ÍđÁ─öÁô■▓╔╝»Í˙╩Í║═NI-DAQmx API╩╣Á├îó─˙Á─Wi-Fi¤ÁŻyĆ─ÄÎ╩«éÇöUŇ╣ÁŻ╔¤░┘éÇďOéńÎâÁ├╩«ĚÍ╚ŢĎÎíúČFď┌─˙┐╔ĎďîóLabVIEW 8.6║═đ┬đ═NI Wi-FiöÁô■▓╔╝»˛îäË│╠đ˛Ë├Ë┌Ďď¤┬ŬË├ţI˲ú║

1íóË├Ë┌ţAťyżSÎoÁ─ÖCø▒OĎĽí¬í¬ÖCøáţĹB▒OĎĽ┐╔ĎďţAĚ└ĎÔ═Ô╩┬╣╩íóâ×╗»ÖCøđď─▄úČ▓óăĎŻÁÁ═đŮ└ÝĽrÚg║═żSÎo│╔▒żíú╩╣Ë├LabVIEW║═Wi-FiŇ˝äËťy┴┐úČ┐╔Ďď┤ˇ┤ˇťp╔┘┼cÖCø▒OĎĽ¤ÓŕPÁ─░▓Đb║═▓╝żÇ│╔▒żíúWi-FiöÁô■▓╔╝»▀Ç║ć╗»┴╦╣PËŤ▒żŰŐ─X║═╗¨Ë┌PCÁ─ĎĂäËČFł÷ď\öÓ¤ÁŻyÁ─ŻĘ┴óíú

2íóŻYśőáţĹBÁ─ď\öÓ▒OĎĽí¬í¬ŻYśőáţĹB▒OĎĽ░Ř└Ę═Ę▀^ěôŢdíóë║┴Ž║═Ćł┴ŽÁ╚͸Ϭͪś╦ĘÍ■║═ś˛┴║Á─đď─▄▀Mđđďu╣└íúË╔Ë┌▀@đęŻYśő│▀┤šŢ^┤ˇúČ╩╣Ë├ËđżÇŻÔŤQĚŻ░Ş│╔▒żŞ▀░║úČ▓óăĎŰyË┌îŹČFíúîŽË┌▀@đę╝░Ăń╦űäËĹBŻYśőťyďçŬË├°ĐďúČŞ▀ÄžîĺÁ─╚źđ┬NI Wi-FiöÁô■▓╔╝»ďOéń╩ă╩╣Ë├LabVIEWď┌żÇĚÍ╬÷úČ▀MđđŇ˝äË║═Ćł┴Žťy┴┐▀B└möÁô■┴¸é¸╦═Á─└ݤŰ▀xô˝íú

3íóşhż│┘|┴┐▒OĎĽí¬í¬şhż│▒OĎĽÁ─ĚÂç˙░Ř└Ę═┴╚└íó╦«║═┐ŇÜÔÁ─═ŕŇűÂ╚Í▒Í┴┼cťěÂ╚║═Ł˝Â╚Ň{╣Ł¤ÓŕPÁ─Ě■äŇø┼cĎÎôpĂĚÁ╚ÍěϬ┘Y«aÁ─╩Ďâ╚âŽ▓ěíú╩╣Ë├LabVIEW║═Wi-FičßŰŐ┼╝║═ŰŐë║ťy┴┐úČŻĘ┴ó░▓Đb┼cÍž│Í║ćć╬Á─čożÇ▀h│╠▒OÂŻŻÔŤQĚŻ░Şíú

łD3ú║─˙┐╔Ďďď┌ÂÓĚNŬË├Íđîóđ┬đ═Wi-FiöÁô■▓╔╝»ďOéń┼cLabVIEWĎ╗Ă╩╣Ë├úČĂńÍđ░Ř└ĘÖCøíóď\öÓ┼cşhż│▒OĎĽíú

LabVIEW 8.6ÍđÁ─Ăń╦űđ┬╠ěđď

│ř┴╦└^└mĎř▀MÂÓ║╦╠Ä└ÝøíóFPGA║═Wi-Fiťy┴┐Á╚Îţđ┬▓óđđ╝╝đgÍ«═ÔúČLabVIEW 8.6▀Ç░Ř└Ę┴╦×ÚÚLĂ┌└¤Ë├ŢîúÚTďOËőÁ─đ┬ď÷╠ěđď║═ÍěϬŞ─▀MíúĎ╗éÇ╩«ĚÍ´@Í°Á─Ş─Îâ╩ă═Ę▀^LabVIEWĂŻ┼_DVD╠Î╝■╦¨ÄžüÝÁ─ŞŘ║├Á─Ë├ޡw˛×úČ╦Ř┤ˇ┤ˇ║ć╗»┴╦LabVIEWÚ_░l¤ÁŻyíóŞŻ╝Ë─úëK║═╣Ąż▀░ŘĎď╝░NI╝Š╚ŢďOéń˛îäË│╠đ˛Á─░▓Đbíúď┌ć╬Ď╗Á─îŽďĺ┐˛ÍđúČ─˙┐╔Ďď░▓ĐbĚÍ▓╝ď┌ÂÓĆłDVD╔¤Á─▄Ť╝■úČ▓óăĎ▒M┐╔─▄╔┘ÁěŞŘôQ├ŻŻÚíú─˙▀Ç┐╔ĎďîŽDVD╔¤╦¨░Ř║ČÁ──˙Ľ║Ľr▓ó▓╗ôÝËđÁ─▄Ť╝■▀Mđđ30╠ýÁ─ďu╣└íú

LabVIEW 8.6▀Ç░Ř└Ę┴╦đ┬ď÷Ú_░l╠ěđďúČ┐╔Ďď╠ߪ▀╣ĄÎ¸đž┬╩úČĂńÍđ░Ř└Ę╚źđ┬Á─│╠đ˛┐˛łDŇű└Ý╣Ąż▀úČÍ╗đŔϬć╬ô˘╩ˇś╦úČż═┐╔Ďď░┤ŇŇLabVIEW´LŞ˝ÍŞ─¤Íđ╦¨Żo│÷Á─żÄ│╠ŻĘÎhîŽ│╠đ˛┐˛łD▀Mđđ┤ˇđíŞ─Îâ║═Íěđ┬┼┼┴đíú╬ĎéâͬÁ└LabVIEW▀x░ňŰSÍ°LabVIEWĂŻ┼_Á─░lŇ╣úČÎâÁ├ďŻüÝďŻĆ═ŰsúČLabVIEW 8.6Ď▓Ďř▀M┴╦┐ý╦┘Ě┼Í├╣Ž─▄úČ─˙┐╔Ďď╩╣Ë├┐╔ţAťyĚŻ╩Ż▀Mđđ▀xô˝úČîŽă░├Š░ň║═│╠đ˛┐˛łDˇ▀Mđđ▓ÚŇĎ║═Ě┼Í├íú

╩└Żš╩ă▓óđđÁ─úČ╣Ą│╠Äč║═┐ĂîW╝Ď▒ěÝÜ─▄ë˛╗¨Ë┌┐╔ÝĹŬÁ─▄Ť╝■úČÚ_░lťy┴┐┼cÎďäË╗»¤ÁŻyíúLabVIEW 8.6┐╔Ďď│ńĚÍ└űË├ÂÓ║╦╠Ä└ÝøíóFPGAĎď╝░Wi-FiöÁô■▓╔╝»ďOéńúČ╦Ř╠ß╣ę┴╦Ë╔ĂńÎď╔ÝłDđ╬╗»żÄ│╠ĂŻ┼_╦¨ÄžüÝÁ─¤Ó═Čâ×Řcí¬í¬čoŇô║╬╚šĆ═ŰsÂ╝┐╔Ďď└űË├Îţđ┬PC╝╝đgÁ──▄┴Žíú

ĘC Michael Neal

Michael Neal╩ăĎ╗╬╗LabVIEW«aĂĚŻŤ└Ýíú╦űź@╚í┴╦Á┬┐╦╦_╦╣┤ˇîWŐW╦╣═íĚÍđúÁ─ŻYśő╣Ą│╠îW╩┐îW╬╗║═╔˙╬´ßtîW╣Ą│╠┤T╩┐îW╬╗íú

Gerardo Garcia╩ăĎ╗╬╗LabVIEWr┼c╣ĄśI┐ěÍĂÁ─▓┐ÚTŻŤ└Ýíú╦űź@Á├┴╦Á┬ÍŢŮrÖC┤ˇîWÁ─ŰŐÎË╣Ą│╠îW╩┐îW╬╗íú

]]>

1 Ş┼╩÷

--- ŰSÍ°FPGA╚Ţ┴┐Á─ď÷┤ˇúČFPGAÁ─ďOËő╚ŇĎŠĆ═ŰsúČďOËőŇ{ďç│╔×ÚĎ╗éÇĚă│úĚ▒ÍěÁ─╚╬äŇíú×Ú┴╦╩╣Á├ďOËő▒M┐ý═Â╚Ű╩đł÷úČďOËő╚╦ćTđŔϬĎ╗ĚN║ćĎÎËđđžÁ─ťyďç╣Ąż▀úČĎď▒M┐╔─▄Á─┐sÂ╠ťyďçĽrÚgíú鸯yÁ─▀ëŢőĚÍ╬÷âxď┌ťyďçĆ═ŰsÁ─FPGAďOËőĽrúČîóĽ■├Š┼RĎď¤┬ÄÎŘcćľţ}ú║1úę╚▒╔┘┐ŇËÓI/OĎř─_íúďOËőÍđø╝■Á─▀xô˝Ď└ô■ďOËőĎÄ─ú°ÂĘúČ═Ę│ú╦¨▀xø╝■Á─I/OĎř─_öÁ─┐║═ďOËőÁ─đŔăˇ╩ăăí║├Ăą┼ńÁ─íú2úęI/OĎř─_ŰyĎďĎř│÷íúďOËőŇ▀×ÚťpđíŰŐ┬Ě░ňÁ─├ŠĚeúČ┤ˇÂ╝▓╔Ë├╝ÜÚgżÓ╣Ą╦ç╝╝đgúČď┌▓╗Ş─äËPCB░ň▓╝żÇÁ─ăÚŤr¤┬Ďř│÷I/OĎř─_Ěă│ú└žŰyíú3úę═ÔŻË▀ëŢőĚÍ╬÷âxËđŞ─äËFPGAďOËőÍđđ┼╠ľďşüÝáţĹBÁ─┐╔─▄úČϲ┤╦ŰyĎď┤_▒úđ┼╠ľÁ─Ňř┤_đďíú4úę鸯yÁ─▀ëŢőĚÍ╬÷âxârŞ˝░║┘FúČîóĽ■╝ËÍěďOËőĚŻÁ─ŻŤŁ˙ěôô˙íú

--- ░ÚŰSÍ°EDA╣Ąż▀Á─┐ý╦┘░lŇ╣úČĎ╗ĚNđ┬Á─Ň{ďç╣Ąż▀Quartus II ÍđÁ─SignalTap II ŁMÎŃ┴╦FPGAĐđ░lÍđË▓╝■Ň{ďçÁ─đŔăˇúČ╦űż▀ËđčoŞ╔ö_íó▒ŃË┌╔ř╝ëíó╩╣Ë├║ćć╬íóârŞ˝Á═┴«Á╚╠ěŘcíú▒ż╬─îóŻÚŻBSignalTap II▀ëŢőĚÍ╬÷âxÁ─͸Ϭ╠ěŘc║═╩╣Ë├┴¸│╠úČ▓óĎďĎ╗éÇîŹ└řŻÚŻBďôĚÍ╬÷âxż▀ˇwÁ─▓┘θ̯ĚĘ║═▓ŻˇEíú

2 SignalTap IIÁ─╠ěŘc╝░╩╣Ë├

--- SignalTap IIăÂ╚Ű▀ëŢőĚÍ╬÷âx╝»│╔ÁŻQuartus IIďOËő▄Ť╝■ÍđúČ─▄ë˛▓ÂÎŻ║═´@╩ż┐╔żÄ│╠ć╬đżĂȤÁŻyúĘSOPCúęďOËőÍđrđ┼╠ľÁ─áţĹBúČ▀@śËĐđ░lŇ▀ż═─▄ď┌ŇűéÇďOËő▀^│╠ÍđĎď¤ÁŻy╝ëÁ─╦┘Â╚Ë^▓ýË▓╝■║═▄Ť╝■Á─Ż╗╗ąÎ¸Ë├íú╦űÍž│ÍÂÓ▀_1024éÇ═ĘÁ└úČ▓╔śË╔ţÂ╚Ş▀▀_128KbúČ├┐éÇĚÍ╬÷âxż¨Ëđ10╝ëË|░lŢö╚Ű/Ţö│÷úČĆ─°ď÷╝Ë┴╦▓╔śËÁ─żźÂ╚íúSignalTap II×ÚďOËőŇ▀╠ß╣ę┴╦śIŻšţI¤╚Á─SOPCďOËőÁ─r┐╔ĎĽđďúČ─▄ë˛┤ˇ┤ˇťp╔┘˛×ÎC▀^│╠Íđ╦¨╗Ę┘MÁ─ĽrÚgíú─┐ă░SignalTap II▀ëŢőĚÍ╬÷âxÍž│ÍÁ─ø╝■¤Á┴đ░Ř└Ęú║APEXT II, APEX20KE, APEX20KC, APEX20K, Cyclone, Excalibur, Mercury, Stratix GX, Stratixíú

--- SignalTap IIîó▀ëŢőĚÍ╬÷─úëKăÂ╚ŰÁŻFPGAÍđúČ╚šłD1╦¨╩żíú▀ëŢőĚÍ╬÷─úëKîŽ┤řťy╣ŁŘcÁ─öÁô■▀Mđđ▓ÂÎŻúČöÁô■═Ę▀^JTAGŻË┐┌Ć─FPGAé¸╦═ÁŻQuartus II▄Ť╝■Íđ´@╩żíú╩╣Ë├SignalTap IIčođŔţ~═ÔÁ─▀ëŢőĚÍ╬÷ďOéńúČÍ╗đŔîóĎ╗ިJTAGŻË┐┌Á─¤┬ŢdŰŐ└|▀BŻËÁŻĎ¬Ň{ďçÁ─FPGAø╝■íúSignalTap IIîŽFPGAÁ─Ďř─_║═â╚▓┐Á─▀BżÇđ┼╠ľ▀Mđđ▓ÂÎŻ║ˇúČîóöÁô■┤ŠâŽď┌Ď╗ÂĘÁ─RAMëKÍđíúϲ┤╦úČđŔϬË├Ë┌▓ÂÎŻÁ─▓╔śËĽršŐđ┼╠ľ║═▒ú┤Š▒╗ťyđ┼╠ľÁ─Ď╗ÂĘŘcöÁÁ─RAMëKíú

--- ╩╣Ë├SignalTap IIÁ─Ď╗░Ń┴¸│╠╩ăú║ďOËő╚╦ćTď┌═ŕ│╔ďOËő▓óżÄÎg╣Ą│╠║ˇúČŻĘ┴óSignalTap II (.stp)╬─╝■▓ó╝Ë╚Ű╣Ą│╠íóďOÍ├STP╬─╝■íóżÄÎg▓ó¤┬ŢdďOËőÁŻFPGAíóď┌Quartus II▄Ť╝■Íđ´@╩ż▒╗ťyđ┼╠ľÁ─▓Ęđ╬íóď┌ťyďç═ŕ«ů║ˇîóďô▀ëŢőĚÍ╬÷âxĆ─ÝŚ─┐Íđäh│říúĎď¤┬├Ŕ╩÷ďOÍ├ SignalTap II ╬─╝■Á─╗¨▒ż┴¸│╠ú║

--- 1ú«ďOÍ├▓╔śËĽršŐíú▓╔śËĽršŐŤQÂĘ┴╦´@╩żđ┼╠ľ▓Ęđ╬Á─ĚÍ▒Š┬╩úČ╦űÁ─ţl┬╩Ϭ┤ˇË┌▒╗ťyđ┼╠ľÁ─ÎţŞ▀ţl┬╩úČĚ˝ätčoĚĘŇř┤_Ě┤Ë│▒╗ťyđ┼╠ľ▓Ęđ╬Á─Îâ╗»íúSignalTap IIď┌ĽršŐ╔¤╔řĐěîó▒╗ťyđ┼╠ľ┤ŠâŽÁŻżĆ┤Šíú

--- 2ú«ďOÍ├▒╗ťyđ┼╠ľíú─▄╩╣Ë├Node Finder ÍđÁ─ SignalTap II ×V▓Ęø▓ÚŇĎ╦¨ËđţAżC║¤║═▓╝żÍ▓╝żÇ║ˇÁ─SignalTap II ╣ŁŘcúČ╠Ý╝ËϬË^▓ýÁ─đ┼╠ľíú▀ëŢőĚÍ╬÷ø▓╗┐╔ťyďçÁ─đ┼╠ľ░Ř└Ęú║▀ëŢőć╬ď¬Á─▀M╬╗đ┼╠ľíóPLLÁ─ĽršŐŢö│÷íóJTAGĎř─_đ┼╠ľíóLVDSúĘÁ═ë║▓ţĚÍúęđ┼╠ľíú

--- 3ú«ďOÍ├▓╔śË╔ţÂ╚íó┤_ÂĘRAMÁ─┤ˇđííúSignalTap II╦¨─▄´@╩żÁ─▒╗ťyđ┼╠ľ▓Ęđ╬Á─ĽrÚgÚLÂ╚×ÚTxúČËő╦Ń╣ź╩Ż╚š¤┬ú║

--- Tx=Ní┴Ts

--- N×ÚżĆ┤ŠÍđ┤ŠâŽÁ─▓╔śËŘcöÁúČTs×Ú▓╔śËĽršŐÁ─Í▄Ă┌íú

--- 4ú«ďOÍ├buffer acquisition modeíúbuffer acquisition mode░Ř└ĘĐşşh▓╔śË┤ŠâŽíó▀B└m┤ŠâŽâ╔ĚN─ú╩ŻíúĐşşh▓╔śË┤ŠâŽĎ▓ż═╩ăĚÍÂ╬┤ŠâŽúČîóŇűéÇżĆ┤ŠĚÍ│╔ÂÓéÇĂČÂ╬(segment)úČ├┐«öË|░lŚl╝■ŁMÎŃĽrż═▓ÂÎŻĎ╗Â╬öÁô■íúďô╣Ž─▄─▄╚ąÁ˘čoŕPÁ─öÁô■úČ╩╣▓╔śËżĆ┤ŠÁ─╩╣Ë├ŞŘ╝Ëý`╗ţíú

--- 5ú«Ë|░l╝ëäeíúSignalTap IIÍž│ÍÂÓË|░l╝ëÁ─Ë|░lĚŻ╩ŻúČÎţÂÓ┐╔Íž│Í10╝ëË|░líú

--- 6ú«Ë|░lŚl╝■íú─▄ďOÂĘĆ═ŰsÁ─Ë|░lŚl╝■Ë├üÝ▓ÂÎŻ¤ÓŬÁ─öÁô■úČĎďůfÍ˙Ň{ďçďOËőíú«öË|░lŚl╝■ŁMÎŃĽrúČď┌signalTapĽršŐÁ─╔¤╔řĐě▓╔śË▒╗ťyđ┼╠ľíú

--- ═ŕ│╔STPďOÍ├║ˇúČîóSTP╬─╝■═ČďşËđÁ─ďOËő¤┬ŢdÁŻFPGAÍđúČď┌Quartus IIÍđSignalTap II┤░┐┌¤┬▓Ú┐┤▀ëŢőĚÍ╬÷âx▓ÂÎŻŻY╣űíúSignalTap II┐╔îóöÁô■═Ę▀^ÂÓËÓÁ─I/OĎř─_Ţö│÷úČĎď╣ę═ÔďOÁ─▀ëŢőĚÍ╬÷ø╩╣Ë├ú╗╗˛Ţö│÷×Úcsvíótblíóvcdíóvwf╬─╝■Ş˝╩ŻĎď╣ęÁ┌╚řĚŻĚ┬ŇŠ╣Ąż▀╩╣Ë├íú

3 îŹ└řĚÍ╬÷

--- ▒ż╬─ĎďĎ╗éÇADC0809ø╝■Á─▓╔śË┐ěÍĂøθ×ÚîŹ└řúČż▀ˇwŇf├¸ď§├┤Ë├SignalTap II üÝ▀MđđFPGAďOËőÁ─˛×ÎCíú╩╣Ë├Altera╣ź╦żÁ─ø╝■Cyclone¤Á┴đFPGA- EP1C12Q240C8úČďôø╝■Íž│ÍSignalTap II ăÂ╚Ű╩Ż▀ëŢőĚÍ╬÷âxÁ─╩╣Ë├íú

--- FPGAÁ─ďOËőŻYśő╚šłD2╦¨╩żíúöÁÎÍ▒ÂţløÁ─▒ÂţlŢö│÷╠ß╣ęADC┐ěÍĂøÁ─▓╔śËË|░l├}Ť_íúA/DŮDôQøADC0809Á─▓┘θĽrđ˛ĎŐöÁô■╩ÍâďúČŞ¨ô■Ăń▓┘θĽrđ˛úČADC┐ěÍĂøüÝîŹČFADC0809Á─öÁô■▓╔╝»▓┘θúČ▓╔śËÁ─ĽrÖCË╔▒ÂţløüÝ┐ěÍĂíú┐ěÍĂø├┐┐ěÍĂ═ŕ│╔Ď╗┤╬▓╔śË▓┘θúČät═úÍ╣Á╚┤ř¤┬Ď╗éÇË|░l├}Ť_Á─ÁŻüÝíú▒Âţlø├┐Ţö│÷Ď╗éÇÁ═ŰŐĂŻ├}Ť_úČADC▓╔śË┐ěÍĂøÁ─áţĹBÖC▀MđđĎ╗┤╬▓╔śË▓┘θíúď┌▒ÂţløÁ─Ë|░l┐ěÍä┬úČ═ŕ│╔▒╗ťyđ┼╠ľĎ╗éÇ╗¨▓ĘÍ▄Ă┌NéÇŘcÁ─Á╚ÚgŞ˘▓╔śËúČ═ČĽröÁÎÍ▒ÂţløŞ˙█ÖŢö╚Űđ┼╠ľÁ─ţl┬╩Á─Îâ╗»úČ▒M┐╔─▄Áě▒ú│ÍNéÇŘcÁ─▓╔śËîĺÂ╚Ňř║├×Ú▒╗ťyđ┼╠ľĎ╗éÇÍ▄▓ĘÁ─îĺÂ╚íú

--- ťyďçÝŚ─┐╩ă╗¨Ë┌FPGAÁ─AD▓╔śË┐ěÍĂøúČ╦ű╩ăË├áţĹBÖC┐ěÍĂÁ─Í▄Ă┌đďÁ─ÍěĆ═╩┬╝■úČĎ╗┤╬▓╔śË▓┘θ═ŕ│╔║ˇÁ╚┤ř▓╔śË├}Ť_íóÚ_╩╝¤┬Ď╗┤╬Á─▓╔śËíúßśîŽ┤řťyÝŚ─┐Á─Í▄Ă┌đďúČ

--- ď┌STP╬─╝■Íđîóbuffer acquisition modeĚÍäeďO×Ú▀B└m┤ŠâŽ║═Đşşh▓╔śË┤ŠâŽâ╔ĚN─ú╩Ż▀Mđđ˛×ÎCíú▀B└m┤ŠâŽĚŻ╩ŻËŤńŤ▓╔śË▓┘θÁ─▀B└m▀^│╠úČ°ď┌Đşşh▓╔śË┤ŠâŽĚŻ╩Ż¤┬SignalTap IIËŤńŤÂÓ┤╬▓╔śËĽr┐╠öÁô■íú

--- ░┤ŇŇ╔¤╩÷SignalTap IIÁ─╩╣Ë├▓ŻˇEúČď┌żÄÎg║ˇÁ─╣Ą│╠Íđ╠Ý╝ËSTP╬─╝■úČ▓óîŽ╬─╝■▀MđđďOÍ├úČ╚šłD3╦¨╩żíú╚š1╠ÄďOÍ├▓╔śËĽršŐct[3]úȤÁŻyĽršŐÁ─16ĚÍţlíú2╠Ä╠Ý╝Ëťyďçđ┼╠ľúČ░Ř└Ę┤řťy─úëKŢö│÷Á─AD▓╔śË┐ěÍĂđ┼╠ľ║═áţĹBÖCÁ─áţĹBÁ╚íú3╠Ä╩ă▓╔śË╔ţÂ╚Á─ďOÍ├úČďO×Ú512íúď┌4╠ÄÁ─ďOÍ├┤_ÂĘ┴╦ď┌clkoĽršŐÁ─╔¤╔řĐěË|░l▀ëŢőĚÍ╬÷âxíúď┌▀B└m┤ŠâŽ─ú╩Ż¤┬ďOÍ├buffer acquisition mode×ÚCirculară░Ë|░l╬╗Í├íúď┌ĚÍÂ╬┤ŠâŽ─ú╩Ż¤┬ďOÍ├×ÚSigmented 512 1 bit segmentsúČ▒Ý╩żîó┤ŠâŽů^äŁĚÍ│╔512éÇÂ╬úČ├┐Â╬1éÇ╬╗Á─┤ŠâŽ╔ţÂ╚íú┤ŠâŽ─ú╩ŻÁ─ďOÍ├╚šłDÍđ6╦¨╩żíú┴Ý═ÔúČ╩╣Ë├Mnemonic TableîóáţĹBÖCÁ─7éÇáţĹBś╦╩ż×ÚÍ▒Ë^├űĚQíú

--- ╩Τ╚îóSTP╬─╝■ďOÍ├│╔▀B└m┤ŠâŽ─ú╩ŻúČ▓óîóďô╬─╝■▀B═Č╣Ą│╠Ď╗ä┬ŢdÁŻFPGAÍđíúď┌▀B└m┤ŠâŽ─ú╩Ż¤┬úČSignalTap IIď┌clkoĽršŐÁ─╔¤╔řĐě▀B└m▓╔śËÍ▒ÁŻ▓╔śËŘcöÁ▀_ÁŻ512éÇíú▀@śËúČSignalTap IIËŤńŤ┴╦Ď╗┤╬▓╔śË▀^│╠Á─╦¨ËđöÁô■úČ▓ÂÎŻŻY╣ű╚šłD4╦¨╩żúČĆ─Íđ─▄┐┤ÁŻFPGA┐ěÍĂADC0809ŮDôQÁ─Ľrđ˛▓Ęđ╬íú

--- îółD3╦¨╩ż▓ŻˇE6ÍđÁ─Buffer acquisition nodeŞ─×ÚSegmentedĚŻ╩ŻúČďOĂńÍÁ×Ú256 1 bit segmentsúČ▓óîóđŮŞ─║ˇÁ─STP╬─╝■▀B═Č╣Ą│╠Íěđ┬¤┬ŢdÁŻFPGAÍđíú║═ć╬┤╬Ë|░l¤Ó═ČÁ─╩ă▀ëŢőĚÍ╬÷âxď┌ADC0809▓╔śËĽršŐ╔¤╔řĐěĽrË|░l▀ëŢőĚÍ╬÷âxúČ▓╗═ČÁ─╩ăϲ×Ú├┐Ď╗Â╬Í╗Ëđ1bitÁ─┤ŠâŽ╔ţÂ╚úČϲ┤╦▓ÂÎŻ1╬╗öÁô■║ˇ▀ëŢőĚÍ╬÷âx═úÍ╣úČÁ╚┤ř¤┬Ď╗┤╬ŁMÎŃË|░lđ┼╠ľď┘┤╬ćóäËúČĎ╗╣▓ćóäË256┤╬íúď┌▓Ęđ╬´@╩ż┤░┐┌úČďO´@╩żŞ˝╩Ż×ÚLine ChartúČ▀@śËŻY╣űż═Í▒Ë^Á─´@╩ż×Ú▀B└mÁ─▓Ęđ╬íúĚÍĂČ▓╔śËúČ┐╔Ë^▓ý═Č▓Ż▓╔śËÁ─ŻY╣űúČłD5╩ă▀B└m▓╔śË256éÇŘcÁ─ŻY╣ű▓Ęđ╬íú

4 ŻYŇô

--- SignalTap II ăÂ╚Ű╩Ż▀ëŢőĚÍ╬÷øúČ╠ß╣ę┴╦đżĂČťyďçÁ─Ď╗éÇĚă│ú║├Á─═żĆŻíú═Ę▀^SignalTap II ťyďçđżĂČčođŔ═ÔŻËîúË├âxøúČ╦űď┌ø╝■â╚▓┐▓ÂÎŻ╣ŁŘc▀MđđĚÍ╬÷║═┼đöÓ¤ÁŻy╣╩Ҥíú▒ż╬─═Ę▀^îŽCyclone EP1C12ø╝■Á─×ÎCîŹďôťyďç╩ÍÂ╬┤ˇ┤ˇ╠ߪ▀¤ÁŻyÁ─Ň{ďç─▄┴ŽúČż▀ËđĚă│ú║├Á─đž╣űíú